瑞萨从授权到自研内核,汽车MCU大厂倒戈RISC-V?

随着芯片IP行业的日新月异的局势,不少芯片大厂都对新的设计架构跃跃欲试。比如汽车MCU大厂瑞萨就在近日宣布,将赶在竞争对手之前,推出第一代自研的32位RISC-VCPU核心,而这一核心未来也将集成到瑞萨的32位MCU上。

率先开始授权RISC-V核心的瑞萨

尽管瑞萨宣布自研RISC-V核心,并打算基于该核心打造全新的MCU产品,但即将到来的新品已经不能算是瑞萨的首个RISC-V产品了。早在 2021年瑞萨发布的RH850/U2B汽车MCU,就集成了一个 RISC-V协处理器DR1000C,而该处理器授权自日本的RISC-V IP厂商NSI-TEXE。

DR1000C作为一个协处理器IP,主要是用于为控制MCU负担高负载的算法处理而设计的,比如模型预测控制、AI推理或传感器数据处理等等,且通过了ISO 26262 ASIL-D的认证。不过RH850/U2B的主要处理核心还是瑞萨自研的RH850 G4MH核心,加上为了车规功能安全而设计的4个锁步核心。

除了与NSI-TEXE达成合作以外,瑞萨还与另外两家RISC-V IP厂商合作共同开发RISC-V解决方案,比如晶心科技和SiFive,尤其是与晶心科技达成了深度合作关系。自2022年起,瑞萨就推出了一系列基于其RISC-V核心打造的产品,比如32bit的ASSP MCU以及64位的RZ/Five MPU。

其中RZ/Five系列通用MPU基于晶心科技的AX45MP内核打造,最高频率可达 1GHz。RZ/Five主要用于物联网终端设备,尤其是需要对传感器数据进行处理的设备,诸如太阳能逆变器、家庭安全网关等。

自研 RISC-V核心及其影响

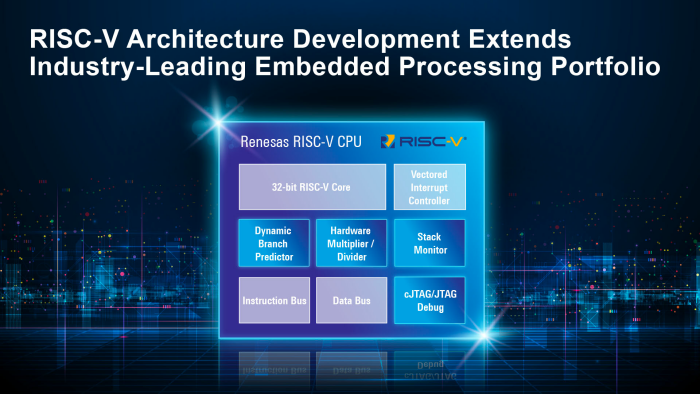

对于全新的自研RISC-V核心,瑞萨并没有透露太多信息,仅提到了该CPU核心可以实现3.27 CoreMark/MHz的性能,单从这个性能指标来看,对标的应该是Arm的Cortex-M4/M3。瑞萨表示该核心可以用作主CPU,或用于管理片上子系统,甚至是集成到ASSP产品中去。

瑞萨自研RISC-V CPU原理图 / 瑞萨电子

对于基于全新RISC-V内核打造的设备,瑞萨表示他们已经开始给选定的客户送样,计划是在明年第一季度正式发布其首个自研RISC-V MCU以及相关开发工具。在 RZ/Five MPU上,瑞萨不仅采用了与Arm MPU RZ/G2UL引脚兼容的设计,也提供了同样符合SMARC标准的评估套件以及板级支持包。这样一来,无论是在哪一平台上开发的应用程序,都可以跨CPU架构完成应用移植。

不过既然瑞萨已经开始自研RISC-V核心,不少人猜测这或许会对晶心科技的业务造成一定影响,不过此类影响应该只局限在32bit的内核上。也就是说受到影响最大的只有采用32位RISC-V 内核N22的ASSP EASY MCU系列,R9A02G020和R9A06G150,两者分别用于电机控制和语音控制HMI应用。

哦! 它是空的。

哦! 它是空的。