**TPS53647** SLUSC39B - JUNE 2015-REVISED FEBRUARY 2017

# TPS53647 4-Phase, D-CAP+, Step-Down, Buck Controller with NVM and PMBus™ Interface for ASIC Power and High-Current Point-of-Load

#### **Features**

- 8-bit Selectable BOOT Voltage via Pinstrap or NVM: 0.5 V to 2.5 V (down to 5-mV Step)

- 1-, 2-, 3-, or 4- Phase Operation

- PMBus™ System Interface for Telemetry of Voltage, Current, Power, Temperature, and Fault Conditions

- 1.8-V and 3.3-V PMBus Bias Compatible

- Fault Reporting: Output Voltage, Output Current, and Temperature

- Configurable with Non-Volatile Memory (NVM) or Resistor Pinstrap

- 16 Levels of Programmable OCP with Pinstrap or NVM

- Fast Transient with DCAP+™Control

- Optimized Efficiency at Light and Heavy Loads

- Support Pre-Bias Startup

- Phase Current Imbalance Detection and Reporting

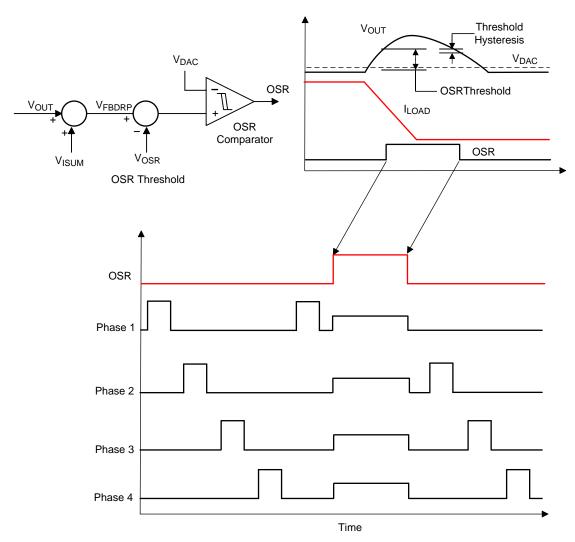

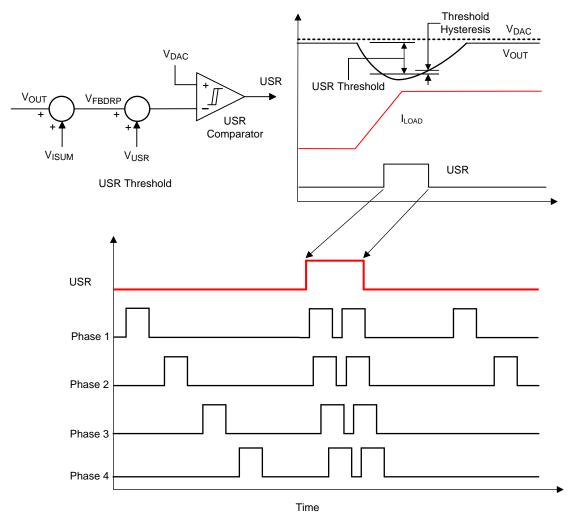

- 8 Independent Levels of Overshoot Reduction (OSR) and Undershoot Reduction (USR)

- Driverless Configuration for Efficient High-Frequency Switching

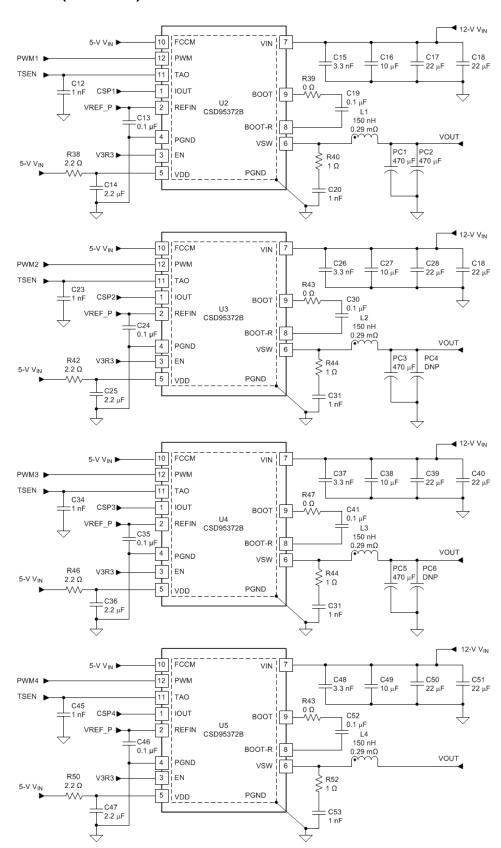

- Fully Compatible with CSD95372BQ5MC NexFET™ Power Stage

- Accurate, Adjustable Voltage Positioning

- 300-kHz to 1-MHz Frequency Selections with Closed-loop Frequency Control

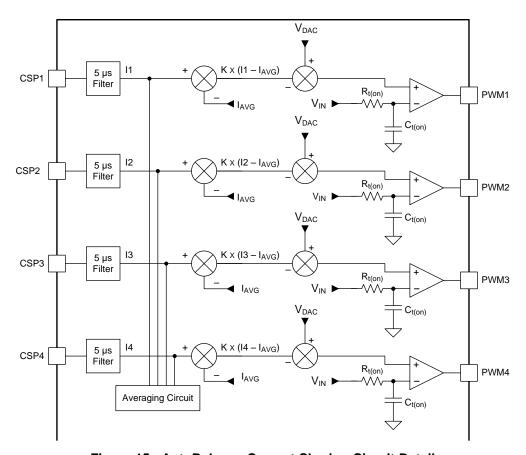

- Patented AutoBalance™ Phase Balancing

- Uses TI's Fusion Digital Power Designer GUI

- Dynamic Phase Shedding with Programmable Current Threshold

- Conversion Voltage Range: 4.5 V to 17 V

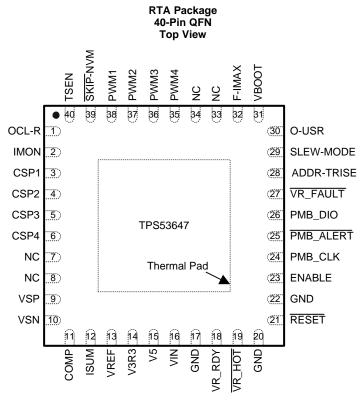

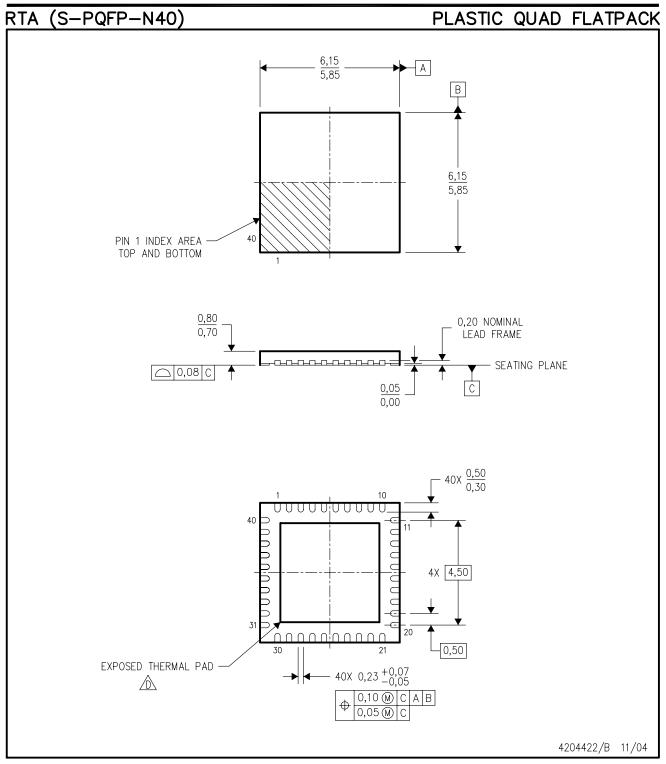

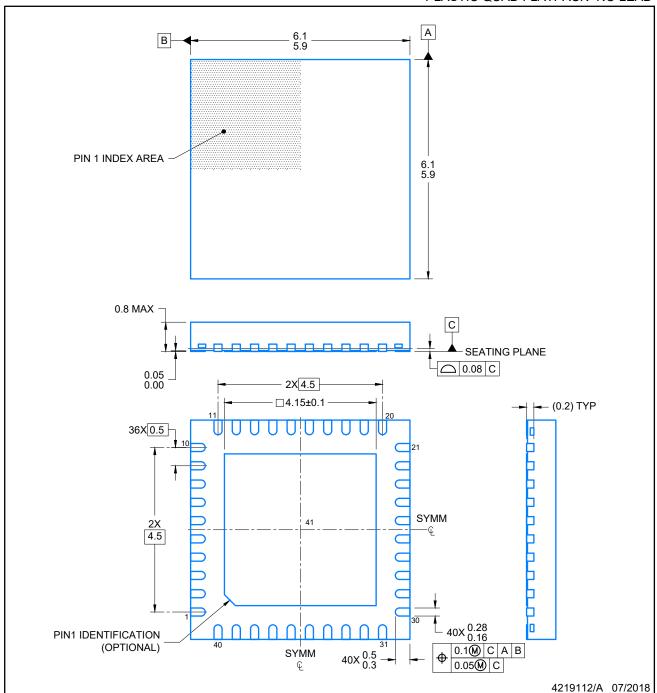

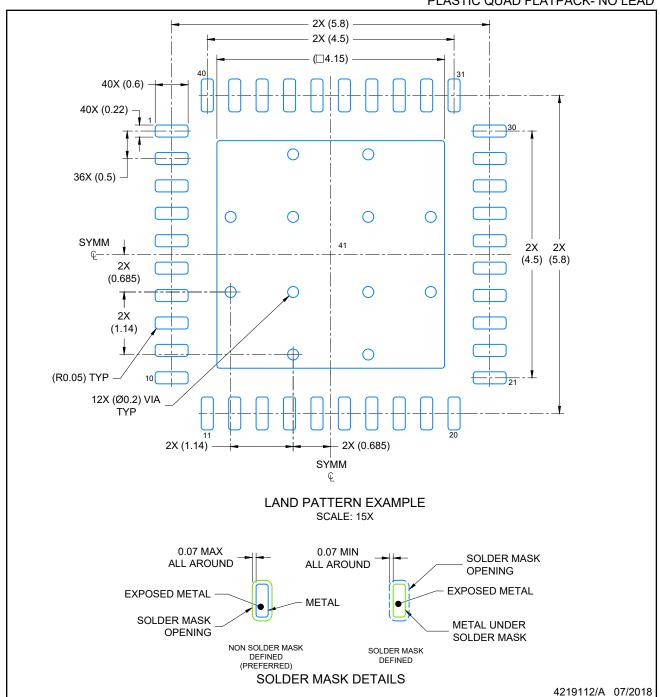

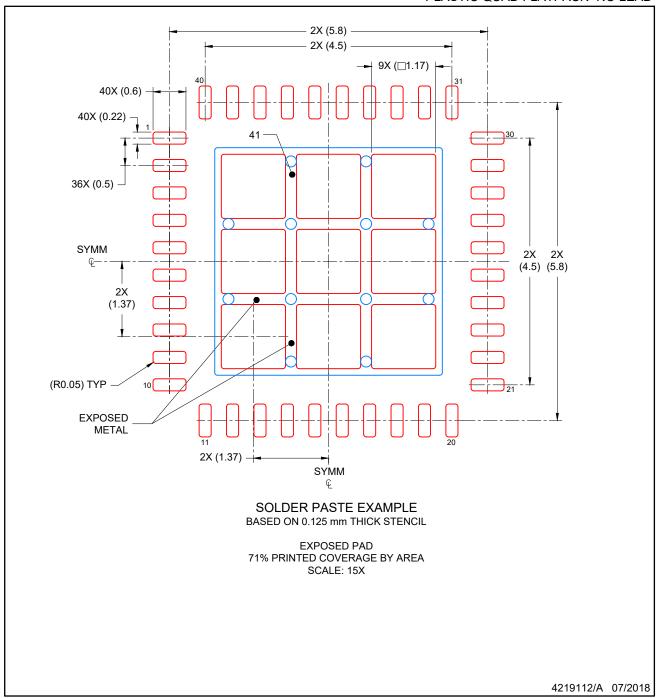

- Small, 6 mm × 6 mm, 40-Pin, QFN, PowerPAD™ Package

# 2 Applications

- Application-Specific Integrated Circuit (ASIC) Power in Communications Equipment

- **High Density Power Solutions**

- Server Power

- **Smart Power Systems**

# 3 Description

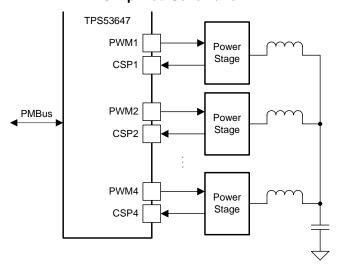

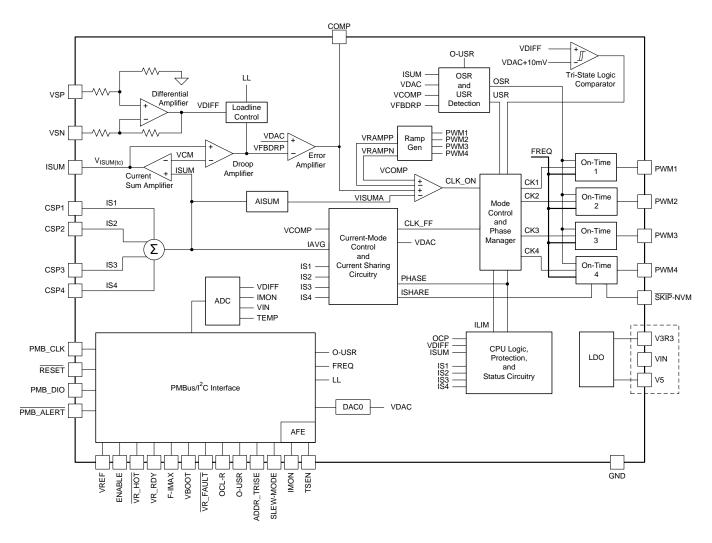

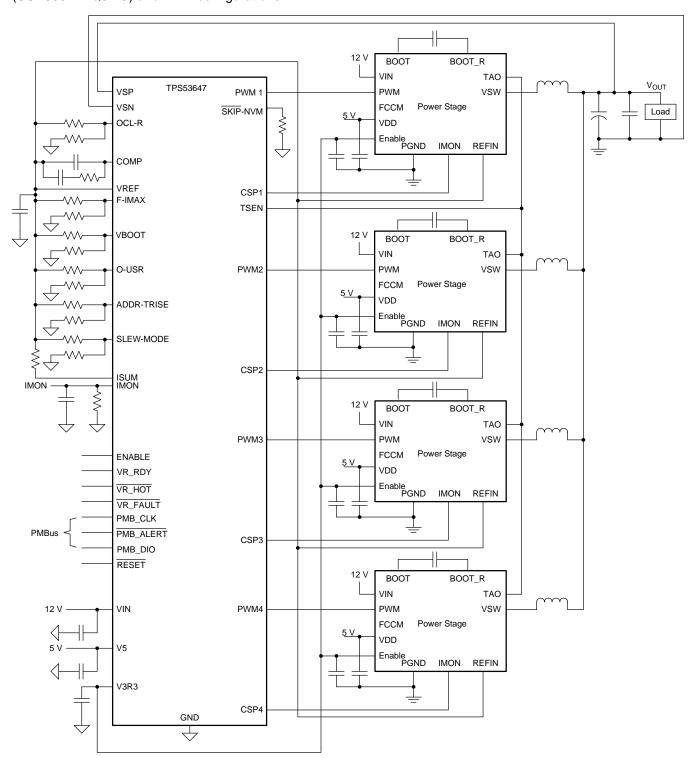

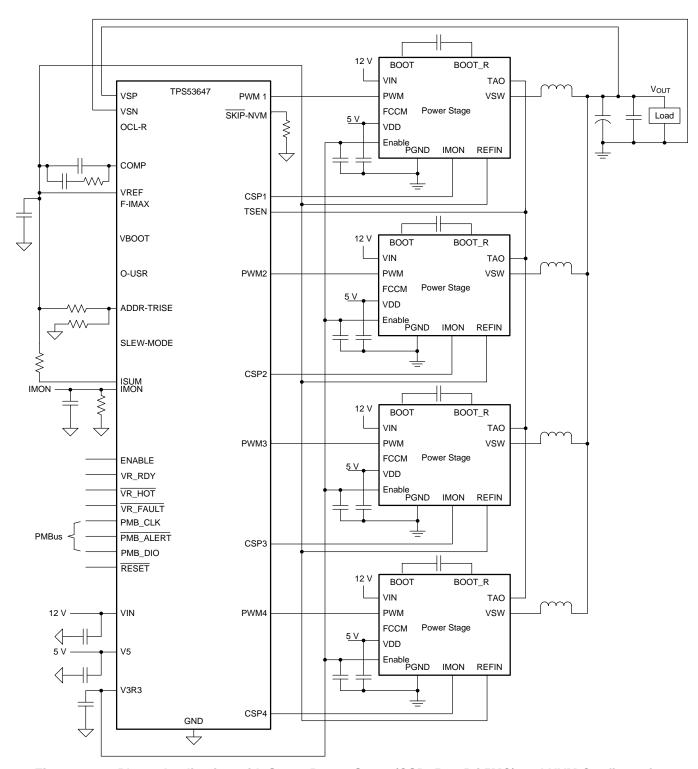

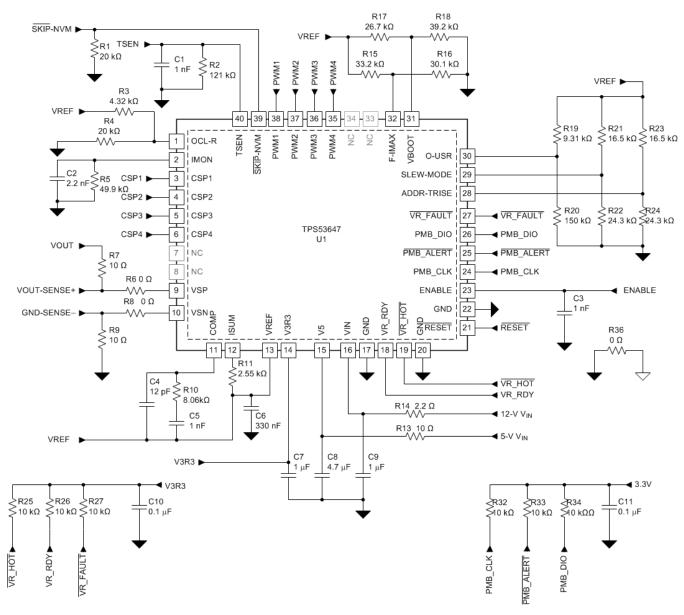

The TPS53647 is a high-current, multi-phase, stepdown controller. The device offers built-in non volatile memory (NVM) and PMBus interface. It is compatible with the NexFET power stages (CSD95372BQ5MC). The TPS53647 provides 8-bit BOOT voltage selection covering output voltage from 0.5 V to 2.5 V, with steps as small as 5 mV, which is ideal for high current application with accurate output voltage setting. Advanced control features such as D-CAP+ architecture with undershoot reduction (USR) and overshoot reduction (OSR) provide fast transient response, lowest output capacitance, and high efficiency. The TPS53647 also provides novel phase interleaving strategy and dynamic phase shedding for efficiency improvement at light loads. In addition, the TPS53647 supports the PMBus communication interface with systems for telemetry of voltage, current, power, temperature, and fault conditions. Some of the configurations can be programmed by pinstrap or PMBus and stored in non-volatile memory to minimize the external component count.

The TPS53647 is offered in a space saving, thermally enhanced 40-pin QFN package and is rated to operate from -40°C to 125°C.

#### Device Information<sup>(1)</sup>

| PART NUMBER | PACKAGE  | BODY SIZE (NOM)   |

|-------------|----------|-------------------|

| TPS53647    | QFN (40) | 6.00 mm × 6.00 mm |

(1) For all available packages, see the orderable addendum at the end of the datasheet.

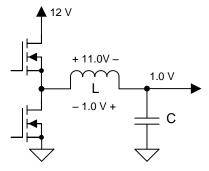

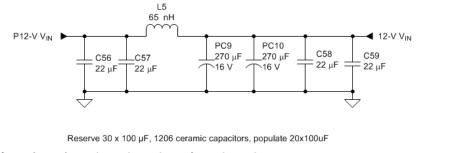

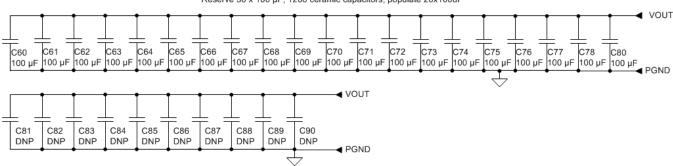

#### Simplified Schematic

# 4 Revision History

| С | changes from Revision A (September 2016) to Revision B                                                                                                                                                                        | Page |

|---|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| • | Updated V3R3 LDO section                                                                                                                                                                                                      | 18   |

| • | Added temperature default value VR_HOT and VR_FAULT Indication section                                                                                                                                                        | 30   |

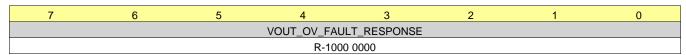

| • | Corrected factory default value of VOUT_OV_FAULT_RESPONSE command in Table 7                                                                                                                                                  | 38   |

| • | Corrected factory default value of VIN_OV_FAULT_LIMIT command in Table 7                                                                                                                                                      | 38   |

| • | Corrected factory default value of MFR_ID command in Table 7                                                                                                                                                                  | 39   |

| • | Corrected factory default value of MFR_SPECIFIC_44 command in Table 7                                                                                                                                                         | 40   |

| С | changes from Original (June 2015) to Revision A                                                                                                                                                                               | Page |

| • | Updated the V <sub>ADDR-TRISE</sub> condition of the PADDR specification in the Electrical Characteristics table from "1.647 V" to "1.615 V"                                                                                  |      |

| • | Updated the V <sub>OCL-R</sub> condition of the I <sub>OCLx</sub> specification in the Electrical Characteristics table from "0.8 V" to "0.85 V"                                                                              | 9    |

| • | Updated the V <sub>OCL-R</sub> condition of the I <sub>OCLx</sub> specification in the Electrical Characteristics table from "1.0 V" to "0.95 V"                                                                              | 9    |

| • | Updated the V <sub>OCL-R</sub> condition of the V <sub>RAMP</sub> specification in the Electrical Characteristics table to "±50 mV"                                                                                           | 9    |

| • | Updated the V <sub>SLEW-MODE</sub> condition of the V <sub>MODE</sub> specification in the Electrical Characteristics table from " 1.647 V with ±20 mV tolerance" to "1.615 V with ±10 mV tolerance"                          |      |

| • | Updated the $V_{O\text{-USR}}$ condition of the $V_{USR}$ specification in the Electrical Characteristics table from " $V_{O\text{-USR}} \ge 1.55 \text{ V}$ (USR OFF)" to "1.55 V $\le V_{O\text{-USR}} \le 1.6 \text{ V}$ " | 11   |

| • | Updated the $V_{VBOOT}$ ( $B_7B_6B_5B_4$ ) condition of the $V_{BOOT}$ specification in the Electrical Characteristics table from " 1.647 V with ±20 mV tolerance" to "1.615 V with ±10 mV tolerance"                         | 12   |

| • | Clarified the READ_VIN (88h) section                                                                                                                                                                                          | 69   |

| • | Corrected typographical error in READ_VOUT (8Bh) section                                                                                                                                                                      | 71   |

| • | Clarified the READ_IOUT (8Ch) section                                                                                                                                                                                         | 71   |

| • | Clarified the READ_TEMPERATURE_1 (8Dh) section                                                                                                                                                                                | 72   |

| • | Clarified the READ_POUT (96h) section                                                                                                                                                                                         | 73   |

| • | Clarified the READ_POUT (96h) section                                                                                                                                                                                         | 74   |

| • | Clarified the MFR_SPECIFIC_04 (Read VOUT) (D4h) section                                                                                                                                                                       | 78   |

| • | Updated the MFR_SPECIFIC_14 (Ramp Height) (DEh) section                                                                                                                                                                       | 86   |

| • | Clarified the Set the Load-Line section                                                                                                                                                                                       | 97   |

| • | Updated Table 79                                                                                                                                                                                                              | 97   |

| • | Updated Table 82                                                                                                                                                                                                              | 98   |

| • | Added Receiving Notification of Documentation Updates section                                                                                                                                                                 | 114  |

| • | Added Community Resources section                                                                                                                                                                                             | 114  |

# 5 Pin Configuration and Functions

NC = No internal connection

## **Pin Functions**

| PIN        |     | VO <sup>(1)</sup> | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                    |  |  |

|------------|-----|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| NAME       | NO. | 1/0               | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                    |  |  |

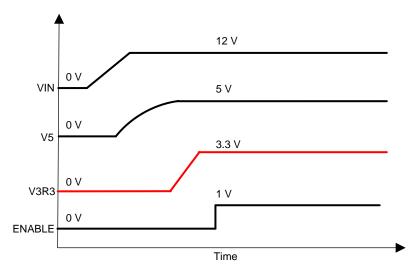

| ADDR-TRISE | 28  | I                 | Voltage divider to VREF pin. A resistor (R <sub>ADDR-TRISE</sub> ) connected between this pin and GND sets the 3-bits. Bit 2 and bit 1 set the rise slew rate. Bit 0 Selects the LSB of BOOT voltage. The voltage (V <sub>ADDR-TRISE</sub> ) sets 4 bits PMBus address. The device latches these settings when V3R3 powers up.                                                 |  |  |

| СОМР       | 11  | 0                 | put of the $g_M$ error amplifier. Resistors and capacitors connected between this pin and the VREF set the compensation.                                                                                                                                                                                                                                                       |  |  |

| CSP1 3     |     |                   |                                                                                                                                                                                                                                                                                                                                                                                |  |  |

| CSP2       | 4   |                   | Positive current sense inputs. Connect to the IOUT pin of TI smart power stages (ex: CSD95372BQ5MC). Tie CSP4, CSP3, or CSP2 to the V3R3 pin according to Table 3 to disable the                                                                                                                                                                                               |  |  |

| CSP3       | 5   | 1                 | corresponding phase.                                                                                                                                                                                                                                                                                                                                                           |  |  |

| CSP4       | 6   |                   |                                                                                                                                                                                                                                                                                                                                                                                |  |  |

| ENABLE     | 23  | I                 | VR enable. 1-V I/O level; 100-ns debounce.                                                                                                                                                                                                                                                                                                                                     |  |  |

| F-IMAX     | 32  | ı                 | Voltage divider to VREF pin. A resistor ( $R_{F\text{-}IMAX}$ ) connected between this pin and GND sets the operating frequency of the controller. The voltage level ( $V_{F\text{-}IMAX}$ ) sets the maximum operating current of the converter. The IMAX value is an 8-bit A/D where $V_{F\text{-}IMAX} = V_{VREF} \times I_{MAX}$ / 255. Both are latched at V3R3 power-up. |  |  |

| GND        | 17  | G                 | Ground pin.                                                                                                                                                                                                                                                                                                                                                                    |  |  |

| GND        | 20  | 0                 | Connect these pine to CND. Note this is not IC around pin                                                                                                                                                                                                                                                                                                                      |  |  |

| GND        | 22  | G                 | Connect these pins to GND. Note this is not IC ground pin.                                                                                                                                                                                                                                                                                                                     |  |  |

<sup>(1)</sup> I = Input, O = Output, P = Power, I/O = Bi-directional, GND = ground

# **Pin Functions (continued)**

| PIN       |     | I/O <sup>(1)</sup> | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|-----------|-----|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME      | NO. | 1/0117             | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

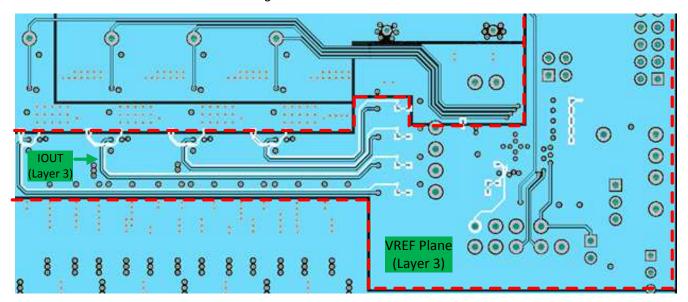

| IMON      | 2   | 0                  | $V_{IMON} = \frac{I_O \times 5 m \Omega \times R_{IMON}}{35 k \Omega}$ Analog current monitor output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

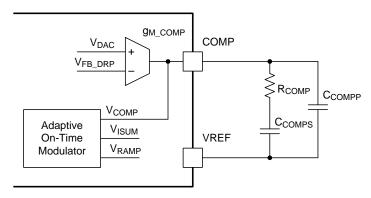

| ISUM      | 12  | 0                  | A resistor (R <sub>ISUM</sub> ) connected between this pin and VREF pin determines the droop. $V_{ISUM} = \frac{I_O \times 5 m\Omega \times g_{M(isum)} \times R_{ISUM}}{n} + V_{REF}$ (where n is the number of phases)                                                                                                                                                                                                                                                                                                                                                                    |

|           | 7   |                    | No. 1 de la companya                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| NO        | 8   | _                  | No connection. Leave the pin open or pull up to V3R3 pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| NC        | 33  |                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|           | 34  | _                  | No connection.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| OCL-R     | 1   | ı                  | A resistor ( $R_{OCL-R}$ ) connected between this pin and GND and the voltage level ( $V_{OCL-R}$ ) select 1 of 16 OCL levels (per phase current-limit). $V_{OCL-R}$ also sets one of four RAMP levels. The device latches these settings when V3R3 powers up.                                                                                                                                                                                                                                                                                                                              |

| O-USR     | 30  | I                  | Voltage divider to VREF pin. A resistor ( $R_{O\text{-USR}}$ ) connected between this pin and GND selects one of seven OSR thresholds or OFF. The voltage level ( $V_{O\text{-USR}}$ ) sets one of seven USR levels or OFF. The device latches these settings when V3R3 powers up.                                                                                                                                                                                                                                                                                                          |

| PMB_ALERT | 25  | 0                  | I <sup>2</sup> C PMBus interrupt line. Open drain. 3.3-V and 1.8-V logic level.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| PMB_CLK   | 24  | 1                  | I <sup>2</sup> C PMBus clock. 3.3-V and 1.8-V logic level.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| PMB_DIO   | 26  | I/O                | I <sup>2</sup> C PMBus digital I/O line. 3.3-V and 1.8-V logic level.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

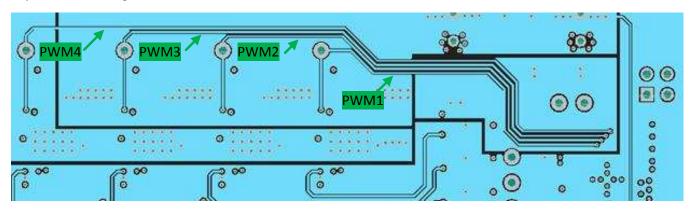

| PWM1      | 38  |                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| PWM2      | 37  | 0                  | PWM signals for each phase                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| PWM3      | 36  |                    | Privitis Signals for each phase                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| PWM4      | 35  |                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

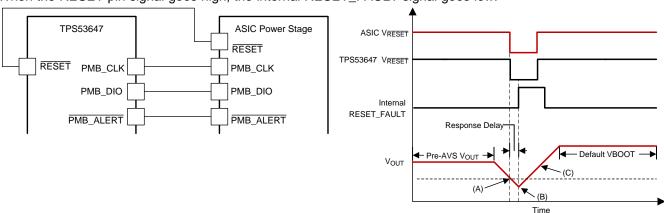

| RESET     | 21  | I                  | Reset pin. If this pin is low for more than 1000 ns, the controller pulls the output voltage to the $V_{\mbox{\footnotesize{BOOT}}}$ level.                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| SKIP-NVM  | 39  | 0                  | A resistor (R <sub>SKIP-NVM</sub> ) connected between this pin and GND sets either pinstrap or NVM configuration mode. This pin can also connect to the FCCM pin of TI smart power stages (ex: CSD95372BQ5MC) for SKIP or FCCM operation.                                                                                                                                                                                                                                                                                                                                                   |

| SLEW-MODE | 29  | I                  | Voltage divider to VREF pin. A resistor (R <sub>SLEW-MODE</sub> ) connected between this pin and GND sets 8 slew rates. The voltage level (V <sub>SLEW-MODE</sub> ) sets 4-bit operation modes. Bit 7 for DAC mode (1 for VR12.0; 0 for VR12.5). Bit 6 for the 4-phase interleaving mode (1 for 1/3 and 2/4 two phase interleaving; 0 for 4 phase interleaving individually). Bit 4 for enabling dynamic phase add or drop (1 for enable; 0 for disable). Bit 3 sets zero load-line (1 for zero load-line; 0 for non-zero load-line) The device latches these settings when V3R3 powers up. |

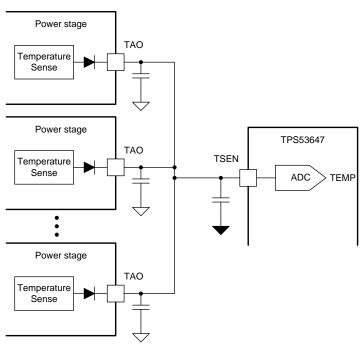

| TSEN      | 40  | I                  | Connect to the TAO/FAULT pin of TI smart power stages (ex: CSD95372BQ5MC) to sense the highest temperature of the power stages and to sense the fault signal from the power stages.                                                                                                                                                                                                                                                                                                                                                                                                         |

| V3R3      | 14  | 0                  | 3.3-V LDO output. Bypass this pin to GND with a ceramic capacitor with a value of 1-µF or larger.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| V5        | 15  | Р                  | 5-V power input. Bypass this pin to GND with a ceramic capacitor with a value of 1-μF or larger. This pin is used to power all internal analog circuits.                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| VBOOT     | 31  | I                  | Voltage divider to VREF pin. A resistor ( $R_{VBOOT}$ ) connected between this pin and GND sets 3 bits (B[3:1]). The voltage level ( $V_{VBOOT}$ ) sets 4 bits (B[7:4]). The total 7 bits set 7 of 8 bits of VID of boot voltage (B[7:1]). The device latches these settings when V3R3 powers up.                                                                                                                                                                                                                                                                                           |

| VIN       | 16  | Р                  | Input voltage supply. This pin is also used for input voltage sensing for on-time control and input undervoltage lockout (UVLO).                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| VR_RDY    | 18  | 0                  | Power good open-drain output for the controller. This pin is typically pulled up to V3R3 pin through a resistor with a value of $3$ -k $\Omega$ or larger.                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| VR_FAULT  | 27  | 0                  | VR fault indicator (open-drain). The failures include shorts of the high-side FETs, over temperature, output overvoltage, and overcurrent conditions of the input. The fault signal should be used on the platform to remove the power source either by firing a shunting SCR to blow a fuse or by turning off the AC power supply. When the failure occurs, the $\overline{VR}$ -FAULT pin is LOW. This pin is typically pulled up to V3R3 pin through a resistor with a value of 3-k $\Omega$ or larger. Leave this pin floating if not used.                                             |

| VR_HOT    | 19  | 0                  | Thermal flag open drain output. Active low. This pin is typically pulled up to V3R3 pin through a resistor with a value of $3-k\Omega$ or larger. Leave this pin floating if not used.                                                                                                                                                                                                                                                                                                                                                                                                      |

Submit Documentation Feedback

Copyright © 2015–2017, Texas Instruments Incorporated

#### Pin Functions (continued)

| PIN         |     | VO <sup>(1)</sup> | DESCRIPTION                                                                                                                                                                                                                               |  |

|-------------|-----|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| NAME        | NO. | 1/0               | DESCRIPTION                                                                                                                                                                                                                               |  |

| VREF        | 13  | 0                 | 1.7-V, 500-μA, LDO reference voltage. Bypass this pin to GND with a ceramic capacitor with a value of 0.33 μF. Connect the VREF pin to the REFIN pin of TI smart power stages (ex: CSD95372BQ5MC) as the current-sense reference voltage. |  |

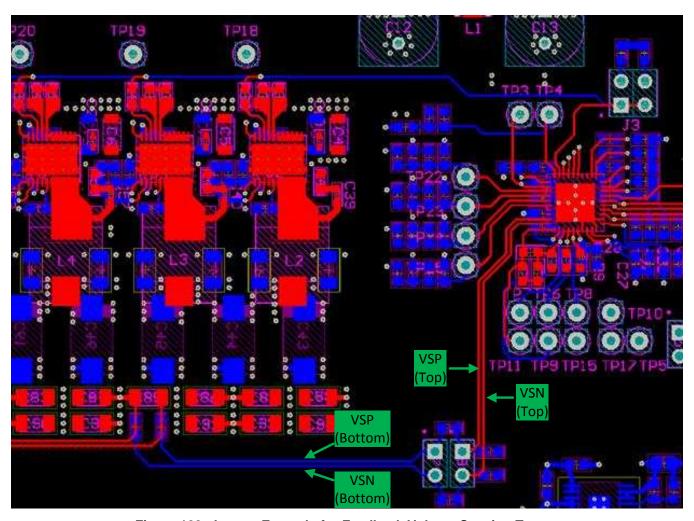

| VSN         | 10  | I                 | Negative input of the remote voltage sense amplifier. Connect this pin directly to the GND of the load.                                                                                                                                   |  |

| VSP         | 9   | I                 | Positive input of the remote voltage sense amplifier. Connect this pin directly to the load.                                                                                                                                              |  |

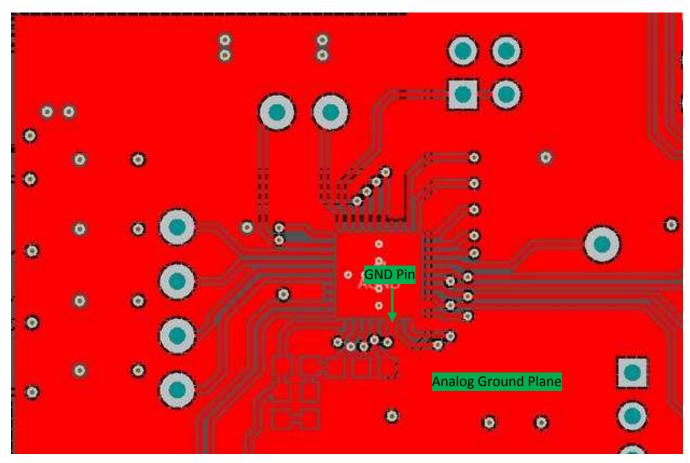

| Thermal Pad |     | GND               | Thermal pad. Connect the thermal pad to the ground plane with multiple vias.                                                                                                                                                              |  |

# 6 Specifications

## 6.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted) (1) (2)

|                    |                                                                                                                  | MIN  | MAX | UNIT |

|--------------------|------------------------------------------------------------------------------------------------------------------|------|-----|------|

|                    | VIN                                                                                                              | -0.3 | 19  |      |

|                    | V5                                                                                                               | -0.3 | 6   |      |

| Input Voltage      | ADDR-TRISE, CSP1, CSP2, CSP3, CSP4, ENABLE, F-IMAX, OCL-R, O-USR, PMB_CLK, PMB_DIO, RESET, SLEW-MODE, VBOOT, VSP | -0.3 | 3.6 | V    |

|                    | TSEN                                                                                                             | -0.3 | 6   |      |

|                    | GND, VSN                                                                                                         | -0.3 | 0.3 |      |

|                    | VREF                                                                                                             | -0.3 | 1.8 |      |

| Output Voltage     | IMON, ISUM, PMB_ALERT, PWM1, PWM2, PWM3, PWM4, SKIP-NVM, V3R3, VR_RDY, VR_FAULT, VR_HOT                          | -0.3 | 3.6 | V    |

|                    | COMP                                                                                                             | -0.3 | 6   |      |

| Operating Junction | Temperature, T <sub>J</sub>                                                                                      | -40  | 150 | °C   |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

(2) All voltage values are with respect to the network ground terminal GND unless otherwise noted.

#### 6.2 Handling Ratings

|                    |                           |                                                                               | MIN         | MAX | UNIT |

|--------------------|---------------------------|-------------------------------------------------------------------------------|-------------|-----|------|

| T <sub>stg</sub>   | Storage temperature range |                                                                               | <b>–</b> 55 | 150 | °C   |

|                    |                           | Human body model (HBM), per ANSI/ESDA/JEDEC JS-001, all pins <sup>(1)</sup>   | -2.5        | 2.5 |      |

| V <sub>(ESD)</sub> | Electrostatic discharge   | Charged device model (CDM), per JEDEC specification JESD22-C101, all pins (2) | -1.5        | 1.5 | kV   |

<sup>(1)</sup> JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

<sup>(2)</sup> JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

# 6.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                |                      |                                                                                   | MIN  | NOM | MAX        | UNIT |

|----------------|----------------------|-----------------------------------------------------------------------------------|------|-----|------------|------|

| Vı             |                      | VIN                                                                               | 4.5  | 12  | 17         |      |

|                |                      | TSEN                                                                              | -0.1 |     | 5.5        |      |

|                |                      | V5                                                                                | 4.5  | 5   | 5.5        |      |

|                | Input voltage        | ADDR-TRISE, F-IMAX, OCL-R, O-USR, SLEW-MODE, VBOOT                                | 0.1  |     | $V_{VREF}$ | V    |

|                |                      | CSP1, CSP2, CSP3, CSP4, VSP                                                       | -0.1 |     | 2.5        |      |

|                |                      | ENABLE, PMB_CLK, PMB_DIO                                                          | -0.1 |     | 3.5        |      |

|                |                      | GND, VSN                                                                          | -0.1 |     | 0.1        |      |

|                |                      | VREF                                                                              | -0.1 |     | 1.72       |      |

|                |                      | V3R3                                                                              | -0.1 | 3.3 | 3.5        |      |

| Vo             | Output voltage       | IMON, ISUM, PMB_ALERT, PWM1, PWM2, PWM3, PWM4, SKIP-NVM, VR_RDY, VR_FAULT, VR_HOT | -0.1 |     | 3.5        | V    |

|                |                      | COMP                                                                              | -0.1 |     | 5.5        |      |

| T <sub>A</sub> | Operating free air t | emperature                                                                        | -40  |     | 125        | °C   |

# 6.4 Thermal Information

|                      |                                              | TPS53647  |       |

|----------------------|----------------------------------------------|-----------|-------|

|                      | THERMAL METRIC <sup>(1)</sup>                | RTA (QFN) | UNIT  |

|                      |                                              | 40 PINS   |       |

| $R_{\theta JA}$      | Junction-to-ambient thermal resistance       | 30.6      |       |

| $R_{\theta JC(top)}$ | Junction-to-case (top) thermal resistance    | 14.2      |       |

| $R_{\theta JB}$      | Junction-to-board thermal resistance         | 6.9       | °C/W  |

| ΨЈТ                  | Junction-to-top characterization parameter   | 0.2       | 10/00 |

| ΨЈВ                  | Junction-to-board characterization parameter | 6.8       |       |

| $R_{\theta JC(bot)}$ | Junction-to-case (bottom) thermal resistance | 1.8       |       |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the IC Package Thermal Metrics application report, SPRA953.

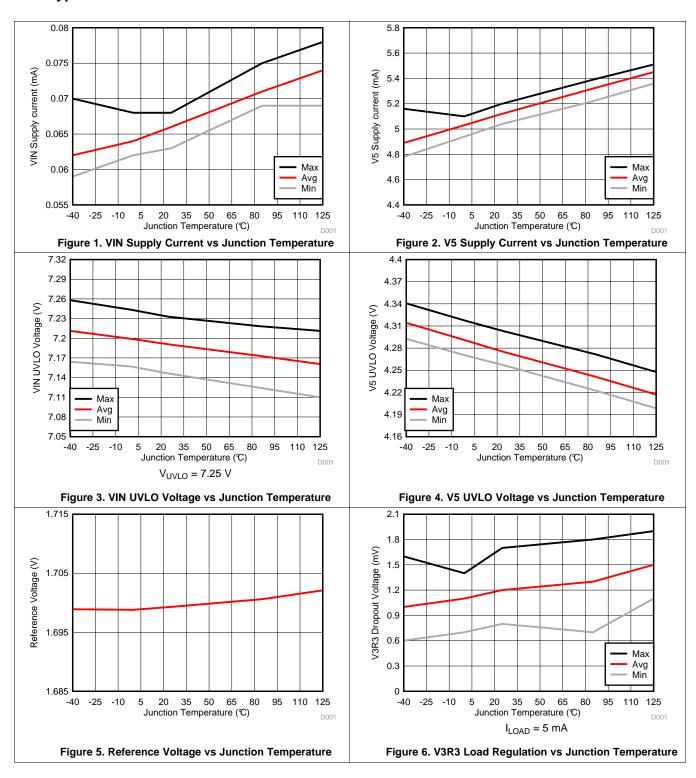

#### 6.5 Electrical Characteristics

over recommended free-air temperature range,  $V_{VIN} = 12 \text{ V}$ ,  $V_{V5} = 5 \text{ V}$ ,  $V_{VSN} = GND$ ,  $V_{VSP} = V_{OUT}$  (unless otherwise noted).

|                            | PARAMETER                             | TEST CONDITIONS                                                                                                                                                        | MIN   | TYP                    | MAX   | UNIT     |

|----------------------------|---------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|------------------------|-------|----------|

| SUPPLY: CUR                | RENTS, UVLO, AND POWER-ON RESET       |                                                                                                                                                                        |       |                        |       |          |

| I <sub>VIN</sub>           | VIN supply current, 4-phase active    | $V_{VDAC} < V_{VSP} < V_{VDAC} + 100 \text{ mV}, \text{ ENABLE} = \text{HI}$                                                                                           |       |                        | 115   | μA       |

| I <sub>V5</sub>            | V5 supply current                     | PMBus Idle, ENABLE = HI                                                                                                                                                |       | 6.1                    | 7     | mA       |

| I <sub>V5SBY</sub>         | V5 standby current                    | ENABLE = LO                                                                                                                                                            |       | 2                      | 2.6   | mA       |

| V <sub>V3R3</sub>          | V3R3 output voltage                   | I <sub>V3R3</sub> = 0 A                                                                                                                                                | 3.2   | 3.3                    | 3.4   | V        |

| V <sub>V3R3(dropout)</sub> | V3R3 load regulation                  | I <sub>V3R3</sub> = 5 mA                                                                                                                                               |       |                        | 100   | mV       |

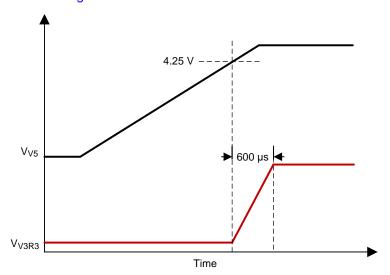

| V <sub>V5UVLOH</sub>       | V5 UVLO OK threshold                  | Ramp up                                                                                                                                                                | 4.1   | 4.25                   | 4.5   | ٧        |

| V <sub>V5UVLOL</sub>       | V5 UVLO fault threshold               | Ramp down                                                                                                                                                              | 3.95  | 4.05                   | 4.25  | V        |

| V <sub>HYS(V5)</sub>       | V5 UVLO hysteresis                    | Hysteresis                                                                                                                                                             | 0.15  | 0.23                   | 0.3   | V        |

|                            | · ·                                   | MFR_SPEC_16[1:0] = 00                                                                                                                                                  | 4.2   | 4.5                    | 4.7   |          |

|                            |                                       | MFR_SPEC_16[1:0] = 01                                                                                                                                                  | 6.9   | 7.25                   | 7.45  |          |

| $V_{VINUVLO}$              | VIN UVLO voltage                      | MFR_SPEC_16[1:0] = 10                                                                                                                                                  | 8.6   | 9.0                    | 9.25  | V        |

|                            |                                       | MFR_SPEC_16[1:0] = 11                                                                                                                                                  | 9.8   | 10.3                   | 10.7  |          |

| V <sub>HYS(VIN)</sub>      | VIN UVLO hysteresis voltage           | Hysteresis voltage                                                                                                                                                     |       | 1                      |       | V        |

|                            | : DAC AND VREF                        | 1,751.151.6                                                                                                                                                            |       |                        |       |          |

|                            |                                       | VR12.5: Change VID0 HI to LO to HI                                                                                                                                     |       | 10                     |       | mV       |

| $V_{VIDSTP}$               | VID Step size                         | VR12.0: Change VID0 HI to LO to HI                                                                                                                                     |       | 5                      |       | mV       |

| V <sub>DAC1</sub>          | Closed Loop VSP tolerance             | VR12.0: 0.61 V $\leq$ V <sub>VSP</sub> $\leq$ 0.995 V, I <sub>OUT</sub> = 0 A, 0 °C $\leq$ T <sub>A</sub> $\leq$ 85 °C                                                 | -6    |                        | 6.5   | mV       |

| V <sub>DAC2</sub>          | Closed Loop VSP tolerance             | $VR12.0: 0.01 V \le V_{VSP} \le 0.003 V, I_{OUT} = 0.4, 0.00 C \le T_{A} \le 0.00 C$ $VR12.0: 1 V \le V_{VSP} \le 1.52 V, I_{COUT} = 0.4, 0.00 C \le T_{A} \le 0.00 C$ | -0.6  |                        | 0.6   | %        |

| V <sub>DAC3</sub>          | Closed Loop VSP tolerance             | VR12.5: $1.50V \le V_{VSP} \le 2.50 \text{ V}$ , $I_{OUT} = 0.4$ , $0.0 \text{ °C} \le T_{A} \le 85 \text{ °C}$                                                        | -1    |                        | 1     | %        |

|                            |                                       | $VR12.0: 0.61 \text{ V} \le V_{VSP} \le 0.995 \text{ V}, I_{OUT} = 0 \text{ A}, -40^{\circ}\text{C} \le T_{A} \le 125$                                                 |       |                        |       |          |

| $V_{DAC4}$                 | Closed Loop VSP tolerance             | °C                                                                                                                                                                     | -8    |                        | 8     | mV       |

| V <sub>DAC5</sub>          | Closed Loop VSP tolerance             | VR12.0: 1.0 V ≤ V <sub>VSP</sub> ≤ 1.52 V, I <sub>OUT</sub> = 0 A, -40 °C ≤ T <sub>A</sub> ≤ 125 °C                                                                    | -0.8  |                        | 8.0   | %        |

| V <sub>DAC6</sub>          | Closed Loop VSP tolerance             | VR12.5: 1.50 V ≤ V <sub>VSP</sub> ≤ 2.50V, I <sub>OUT</sub> = 0 A, -40°C ≤ T <sub>A</sub> ≤ 125 °C                                                                     | -1.1  |                        | 1.0   | %        |

| $V_{VREF}$                 | VREF output                           | 4.5 ≤ V <sub>V5</sub> ≤ 5.5 V, I <sub>VREF</sub> = 0 A                                                                                                                 | 1.685 | 1.70                   | 1.717 | V        |

| V <sub>VREFSRC</sub>       | VREF output source                    | I <sub>VREF</sub> = 0 to 500 μA                                                                                                                                        | -4    | -1                     |       | mV       |

| V <sub>VREFSNK</sub>       | VREF output sink                      | I <sub>VREF</sub> = -500 to 0 μA                                                                                                                                       |       | 1                      | 4     | mV       |

| CURRENT SEI                | NSE: AMPLIFIER AND PHASE BALANCING    |                                                                                                                                                                        |       |                        |       |          |

| G <sub>CSINT</sub>         | Internal current sense gain           | Gain from (CSPx – VREF ) to PWM comparator                                                                                                                             |       | 1.0                    |       | V/V      |

| COMPENSATO                 | DR: VOLTAGE POSITIONING AND AMPLIFIER | 1                                                                                                                                                                      |       |                        | 1     |          |

| g <sub>M(isum)</sub>       | ISUM amplifier transconductance       | V <sub>VSP</sub> = 1.7 V                                                                                                                                               |       | 500                    |       | μS       |

| g <sub>M(comp)</sub>       | COMP amplifier transconductance       | V <sub>VSP</sub> = 1.7 V                                                                                                                                               |       | 1000                   |       | μS       |

| V <sub>CCLAMPN</sub>       | COMP amplifier negative clamp voltage | (V <sub>VREF</sub> - V <sub>COMP</sub> )                                                                                                                               |       | V <sub>RAMP</sub> + 20 |       | mV       |

| V <sub>CCLAMPP</sub>       | COMP amplifier positive clamp voltage | (V <sub>COMP</sub> - V <sub>VREF</sub> )                                                                                                                               | 2.1   | 2.2                    | 2.3   | V        |

|                            | NSE: VSP AND VSN                      |                                                                                                                                                                        |       |                        |       |          |

| I <sub>VSP</sub>           | VSP input bias current                | Not in fault, disable or UVLO, $V_{VSP} = V_{VDAC} = 2.3 \text{ V}, V_{VSN} = 0 \text{ V}$                                                                             |       |                        | 300   | μΑ       |

| I <sub>VSN</sub>           | VSN input bias current                | Not in fault, disable or UVLO, $V_{VSP} = V_{VDAC} = 2.3 \text{ V}, V_{VSN} = 0 \text{ V}$                                                                             | -30   | -23                    |       | μΑ       |

| R <sub>SFTSTP</sub>        | Transistor resistance                 | Connect to VSP                                                                                                                                                         |       | 10                     |       | kΩ       |

|                            | T, VR_RDY, VR_FAULT, VR_HOT, AND ENA  | BLE) INTERFACE PINS: I/O VOLTAGE AND CURRENT                                                                                                                           |       |                        |       |          |

| R <sub>RPGDL</sub>         | Open drain pull-down resistance       | VR_RDY, pulldown resistance at 0.31 V                                                                                                                                  |       | 36                     | 50    | Ω        |

| I <sub>VRTTLK</sub>        | Open drain leakage current            | VR_HOT, VR_RDY, hi-Z leakage, apply 3.3 V in off state                                                                                                                 | -2    | 0.2                    | 2     | μA       |

| V <sub>RSTL</sub>          | RESET logic low                       | RESET Pin                                                                                                                                                              |       |                        | 0.8   | V        |

| V <sub>RSTH</sub>          | RESET logic high                      | RESET Pin                                                                                                                                                              | 1.2   |                        |       | V        |

| T <sub>RSTTDLY</sub>       | RESET Delay Time                      |                                                                                                                                                                        |       | 1                      |       | μs       |

| V <sub>ENL</sub>           | ENABLE logic low                      |                                                                                                                                                                        |       |                        | 0.3   | V        |

| V <sub>ENH</sub>           | ENABLE logic high                     |                                                                                                                                                                        | 0.8   |                        |       | V        |

| I <sub>ENH</sub>           | I/O 1.1- V leakage                    | Leakage current , V <sub>ENABLE</sub> = 1.1 V                                                                                                                          |       |                        | 25    | μA       |

|                            | FACE PINS: I/O VOLTAGE AND CURRENT    | C 11 1/1 ENRULE 1                                                                                                                                                      |       |                        |       | <b>P</b> |

| V <sub>PMBL</sub>          | PMBus pins logic low                  |                                                                                                                                                                        |       |                        | 0.8   | V        |

| V <sub>PMBH</sub>          | PMBus pins logic high                 |                                                                                                                                                                        | 1.2   |                        | 0.0   | V        |

| I <sub>PMBL</sub>          | Logic low input current               | V <sub>PMBus</sub> =0 V                                                                                                                                                | -10   |                        | 10    | μA       |

|                            | Logic high input current              | V <sub>PMBus</sub> =1.8 V                                                                                                                                              | -10   |                        | 10    | μА       |

| PMBH                       | Logic mgm mpat carrent                | *PMBus= ··· V                                                                                                                                                          | -10   |                        | 10    | μA       |

over recommended free-air temperature range,  $V_{VIN} = 12 \text{ V}$ ,  $V_{VS} = 5 \text{ V}$ ,  $V_{VSN} = GND$ ,  $V_{VSP} = V_{OUT}$  (unless otherwise noted).

|                                        | PARAMETER                                                                                | TEST CONDITIONS                                                                                                                                                                                                                                                                             | MIN TYP | MAX | UNIT |

|----------------------------------------|------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|-----|------|

| ADDR-TRISE                             | PIN: PMBUS ADDRESS, SOFT START RISE T                                                    | ME SETTING                                                                                                                                                                                                                                                                                  |         |     |      |

|                                        |                                                                                          | $R_{ADDR-TRISE} \le 20 \text{ k}\Omega \text{ or } R_{ADDR-TRISE} = 24 \text{ k}\Omega \text{ or } MFR\_SPEC\_12<1:0> = 00b$                                                                                                                                                                | 1       |     |      |

| ADDR-TRISE PIN SL <sub>RISE</sub> BOOT | Soft start rise slew rate in terms of V <sub>OUT</sub>                                   | $R_{ADDR-TRISE}$ = 30 k $\Omega$ or $R_{ADDR-TRISE}$ = 39 k $\Omega$ or MFR_SPEC_12<1:0> = 01b                                                                                                                                                                                              | 1/2     |     |      |

| SLRISE                                 | slew rate                                                                                | $R_{ADDR-TRISE}$ = 56 k $\Omega$ or $R_{ADDR-TRISE}$ = 75 k $\Omega$ or MFR_SPEC_12<1:0> = 10b                                                                                                                                                                                              | 1/4     |     |      |

| 300T                                   |                                                                                          | R <sub>ADDR-TRISE</sub> = 100 kΩ or R <sub>ADDR-TRISE</sub> = 150 kΩ or MFR_SPEC_12<1:0> = 11b                                                                                                                                                                                              | 1/8     |     |      |

| POOT                                   | BOOT voltage set (B0)                                                                    | $\begin{aligned} R_{ADDR\text{-}TRISE} &\leq 20 \text{ k}\Omega \text{ or } R_{ADDR\text{-}TRISE} = 30 \text{ k}\Omega \text{ or } R_{ADDR\text{-}TRISE} = 56 \\ \text{k}\Omega \text{ or } R_{ADDR\text{-}TRISE} &= 100 \text{ k}\Omega, \text{ or MFR\_SPEC\_11} [0] &= 0b \end{aligned}$ | 0       |     |      |

| БООТ                                   | BOOT voltage set (B0)                                                                    | $\begin{split} R_{ADDR\text{-}TRISE} &= 24 \text{ k}\Omega \text{ or } R_{ADDR\text{-}TRISE} = 39 \text{ k}\Omega \text{ or } R_{ADDR\text{-}TRISE} = 75 \\ \text{k}\Omega \text{ or } R_{ADDR\text{-}TRISE} &= 150 \text{ k}\Omega, \text{ or MFR\_SPEC\_11} [0] = 1b \end{split}$         | 1       |     |      |

|                                        |                                                                                          | V <sub>ADDR-TRISE</sub> ≤ 0.053 V with ±20 mV tolerance                                                                                                                                                                                                                                     | 1100000 |     |      |

|                                        |                                                                                          | V <sub>ADDR-TRISE</sub> = 0.159 V with ±20 mV tolerance                                                                                                                                                                                                                                     | 1100001 |     |      |

|                                        |                                                                                          | V <sub>ADDR-TRISE</sub> = 0.266 V with ±20 mV tolerance                                                                                                                                                                                                                                     | 1100010 |     |      |

|                                        |                                                                                          | V <sub>ADDR-TRISE</sub> = 0.372 V with ±20 mV tolerance                                                                                                                                                                                                                                     | 1100011 |     |      |

|                                        |                                                                                          | V <sub>ADDR-TRISE</sub> = 0.478 V with ±20 mV tolerance                                                                                                                                                                                                                                     | 1100100 |     |      |

|                                        |                                                                                          | V <sub>ADDR-TRISE</sub> = 0.584 V with ±20 mV tolerance                                                                                                                                                                                                                                     | 1100101 |     |      |

|                                        |                                                                                          | V <sub>ADDR-TRISE</sub> = 0.691 V with ±20 mV tolerance                                                                                                                                                                                                                                     | 1100110 |     |      |

| DADDD                                  | DMD::: address hits set (44D OD D D )                                                    | V <sub>ADDR-TRISE</sub> = 0.797 V with ±20 mV tolerance                                                                                                                                                                                                                                     | 1100111 |     |      |

| PADDR                                  | PMBus address bits set (11P <sub>4</sub> 0P <sub>2</sub> P <sub>1</sub> P <sub>0</sub> ) | V <sub>ADDR-TRISE</sub> = 0.903 V with ±20 mV tolerance                                                                                                                                                                                                                                     | 1110000 |     |      |

|                                        |                                                                                          | V <sub>ADDR-TRISE</sub> = 1.009 V with ±20 mV tolerance                                                                                                                                                                                                                                     | 1110001 |     |      |

|                                        |                                                                                          | V <sub>ADDR-TRISE</sub> = 1.116 V with ±20 mV tolerance                                                                                                                                                                                                                                     | 1110010 |     |      |

|                                        |                                                                                          | V <sub>ADDR-TRISE</sub> = 1.222 V with ±20 mV tolerance                                                                                                                                                                                                                                     | 1110011 |     |      |

|                                        |                                                                                          | V <sub>ADDR-TRISE</sub> = 1.328 V with ±20 mV tolerance                                                                                                                                                                                                                                     | 1110100 |     |      |

|                                        |                                                                                          | V <sub>ADDR-TRISE</sub> = 1.434 V with ±20 mV tolerance                                                                                                                                                                                                                                     | 1110101 |     |      |

|                                        |                                                                                          | V <sub>ADDR-TRISE</sub> = 1.541 V with ±20 mV tolerance                                                                                                                                                                                                                                     | 1110110 |     |      |

|                                        |                                                                                          | V <sub>ADDR-TRISE</sub> = 1.615 V with ±10 mV tolerance                                                                                                                                                                                                                                     | 1110111 |     |      |

over recommended free-air temperature range,  $V_{VIN} = 12 \text{ V}$ ,  $V_{VS} = 5 \text{ V}$ ,  $V_{VSN} = GND$ ,  $V_{VSP} = V_{OUT}$  (unless otherwise noted).

|                   | PARAMETER                                           | TEST CONDITIONS                                                                                                                                                       | MIN | TYP | MAX | UNIT          |

|-------------------|-----------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|---------------|

| OCL-R PIN:        | OVERCURRENT THRESHOLDS AND RAMP                     | SETTINGS                                                                                                                                                              |     |     |     |               |

|                   |                                                     | $R_{OCL-R} = 20$ kΩ and $V_{OCL-R} \le 0.85$ V or MFR_SPEC_00[3:0] = 0000b                                                                                            | 21  | 24  | 27  |               |

|                   |                                                     | $R_{OCL-R} = 24 \text{ k}\Omega$ and $V_{OCL-R} \le 0.85 \text{ V}$ or MFR_SPEC_00[3:0] = 0001b                                                                       | 25  | 27  | 30  |               |

|                   |                                                     | $R_{OCL-R} = 30 \text{ k}\Omega$ and $V_{OCL-R} \leq 0.85 \text{ V}$ or MFR_SPEC_00[3:0] = 0010b                                                                      | 28  | 30  | 33  |               |

|                   |                                                     | $R_{OCL.R} = 39 \text{ k}\Omega$ and $V_{OCL.R} \le 0.85 \text{ V}$ or MFR_SPEC_00[3:0] = 0011b                                                                       | 31  | 33  | 36  |               |

| l <sub>octx</sub> |                                                     | $R_{OCL-R} = 56 \text{ k}\Omega$ and $V_{OCL-R} \le 0.85 \text{ V}$ or MFR_SPEC_00[3:0] = 0100b                                                                       | 34  | 36  | 39  |               |

|                   |                                                     | $R_{OCL-R} = 75 \text{ k}\Omega$ and $V_{OCL-R} \le 0.85 \text{ V}$ or MFR_SPEC_00[3:0] = 0101b                                                                       | 37  | 39  | 42  |               |

|                   |                                                     | $R_{\rm OCL-R}$ = 100 k $\Omega$ and $V_{\rm OCL-R}$ ≤ 0.85 V or MFR_SPEC_00[3:0] = 0110b                                                                             | 40  | 42  | 45  |               |

|                   | Phase OCL level (CSPx-VREF)                         | $R_{OCL-R}$ ≥ 150 kΩ and $V_{OCL-R}$ ≤ 0.85 V or MFR_SPEC_00[3:0] = 0111b                                                                                             | 43  | 45  | 48  | ۸             |

|                   | (valley current-limit)                              | $R_{OCL-R} = 20 \text{ k}\Omega$ and $V_{OCL-R} \ge 0.95 \text{ V}$ or MFR_SPEC_00[3:0] = 1000b                                                                       | 46  | 48  | 51  | А             |

|                   |                                                     | $R_{OCL-R} = 24 \text{ k}\Omega$ and $V_{OCL-R} \ge 0.95 \text{ V}$ or MFR_SPEC_00[3:0] = 1001b                                                                       | 49  | 51  | 54  |               |

|                   |                                                     | $R_{OCL-R} = 30 \text{ k}\Omega$ and $V_{OCL-R} \ge 0.95 \text{ V}$ or MFR_SPEC_00[3:0] = 1010b                                                                       | 52  | 54  | 57  |               |

|                   |                                                     | $R_{OCL-R} = 39 \text{ k}\Omega$ and $V_{OCL-R} \ge 0.95 \text{ V}$ or MFR_SPEC_00[3:0] = 1011b                                                                       | 55  | 57  | 60  |               |

|                   |                                                     | $R_{OCL-R} = 56 \text{ k}\Omega$ and $V_{OCL-R} \ge 0.95 \text{ V}$ or MFR_SPEC_00[3:0] = 1100b                                                                       | 58  | 60  | 63  |               |

|                   |                                                     | $R_{OCL-R} = 75 \text{ k}\Omega$ and $V_{OCL-R} \ge 0.95 \text{ V}$ or MFR_SPEC_00[3:0] = 1101b                                                                       | 61  | 63  | 66  |               |

|                   |                                                     | $R_{OCL-R}$ = 100 k $\Omega$ and $V_{OCL-R}$ ≥ 0.95 V or MFR_SPEC_00[3:0] = 1110b                                                                                     | 64  | 66  | 69  |               |

|                   |                                                     | $R_{OCL-R}$ ≥ 150 k $\Omega$ and $V_{OCL-R}$ ≥ 0.95 V or MFR_SPEC_00[3:0] = 11111b                                                                                    | 67  | 69  | 72  |               |

| $V_{RAMP}$        | Ramp setting                                        | $V_{OCL-R} = 0.2 \text{ V } \pm 50 \text{mV} \text{ or } V_{OCL-R} = 1.0 \text{ V } \pm 50 \text{mV} \text{ or } MFR\_SPEC\_14[2:0] = 001b$                           | 30  | 40  | 50  | $mV_{P_{-}P}$ |

|                   |                                                     | $V_{OCL-R}$ = 0.4 V ±50mV or $V_{OCL-R}$ = 1.2 V ±50mV or MFR_SPEC_14[2:0] = 011b                                                                                     | 70  | 80  | 90  |               |

|                   |                                                     | $V_{OCL-R} = 0.6 \text{ V } \pm 50 \text{mV or } V_{OCL-R} = 1.4 \text{ V } \pm 50 \text{mV or } \text{MFR\_SPEC\_14[2:0]} = 110 \text{b}$                            | 135 | 145 | 155 |               |

|                   |                                                     | $V_{\rm OCL-R}$ = 0.8 V ±50mV or $V_{\rm OCL-R}$ = 1.6 V ±50mV or MFR_SPEC_14[2:0] = 111b                                                                             | 180 | 190 | 205 |               |

| F-IMAX PIN:       | FREQUENCY AND IMAX SETTINGS                         |                                                                                                                                                                       |     |     |     |               |

| f <sub>sw</sub>   | Switching frequency (See Switching Characteristics) |                                                                                                                                                                       |     |     |     |               |

|                   |                                                     | $V_{F\text{-IMAX}(min)} = 0.136V$<br>$I_{MAX} = (V_{F\text{-IMAX}} / V_{VREF} \times 256) - 0.5$                                                                      | 18  | 20  | 22  |               |

|                   | IMAX values                                         | $\begin{split} V_{F\text{-IMAX}(min)} &= 0.403 \text{ V} \\ I_{MAX} &= & (V_{F\text{-IMAX}} / V_{VREF} \times 256) \text{-} 0.5 \end{split}$                          | 58  | 60  | 62  | А             |

| I <sub>MAX</sub>  | IIVITA VAIGES                                       | $\begin{aligned} V_{\text{F-IMAX}(\text{min})} &= 0.536 \text{ V} \\ I_{\text{MAX}} &= & (V_{\text{F-IMAX}} / V_{\text{VREF}} \times 256) \text{-} 0.5 \end{aligned}$ | 78  | 80  | 82  | ^             |

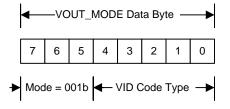

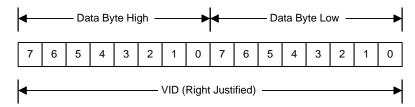

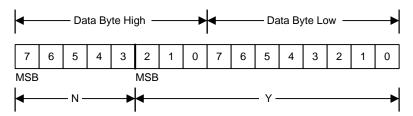

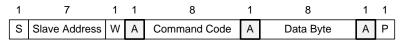

|                   |                                                     | $V_{F\text{-IMAX}(min)} = 0.803 \text{ V}$ $I_{MAX} = (V_{F\text{-IMAX}} / V_{VREF} \times 256) - 0.5$                                                                | 118 | 120 | 122 |               |