# **Cyclone IV Device Handbook,**

## Volume 1

101 Innovation Drive San Jose, CA 95134 www.altera.com

© 2016 Altera Corporation. All rights reserved. ALTERA, ARRIA, CYCLONE, HARDCOPY, MAX, MEGACORE, NIOS, QUARTUS and STRATIX words and logos are trademarks of Altera Corporation and registered in the U.S. Patent and Trademark Office and in other countries. All other words and logos identified as trademarks or service marks are the property of their respective holders as described at www.altera.com/common/legal.html. Altera warrants performance of its semiconductor products to current specifications in accordance with Altera's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Altera assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Altera. Altera customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services.

ISO 9001:2008 Registered

## **Contents**

| Chapter Revision Dates                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | ix     |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|

| Additional Information                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Info-1 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |        |

| Cyclone IV Device Family Features Device Resources Package Matrix Cyclone IV Device Family Speed Grades Cyclone IV Device Family Architecture FPGA Core Fabric I/O Features Clock Management External Memory Interfaces Configuration High-Speed Transceivers (Cyclone IV GX Devices Only) Hard IP for PCI Express (Cyclone IV GX Devices Only) Reference and Ordering Information Document Revision History  apter 2. Logic Elements and Logic Array Blocks in Cyclone IV Devices Le Features LE Features LE Operating Modes Normal Mode Arithmetic Mode Logic Array Blocks Topology LAB Interconnects LAB Control Signals Document Revision History  apter 3. Memory Blocks in Cyclone IV Devices Overview Control Signals |        |

| Chapter 1. Cyclone IV FPGA Device Family Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |        |

| Cyclone IV Device Family Features                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |        |

| Device Resources                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 1–3    |

| Package Matrix                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 1–5    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |        |

| Logic Elements                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |        |

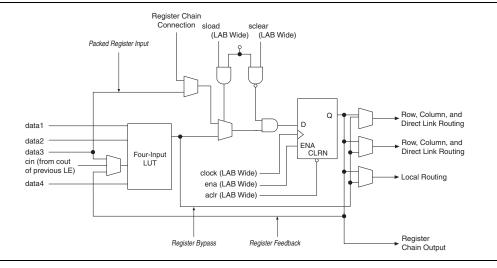

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |        |

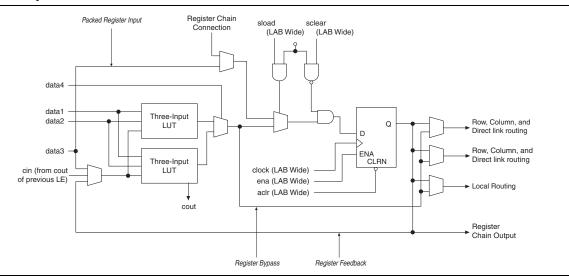

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |        |

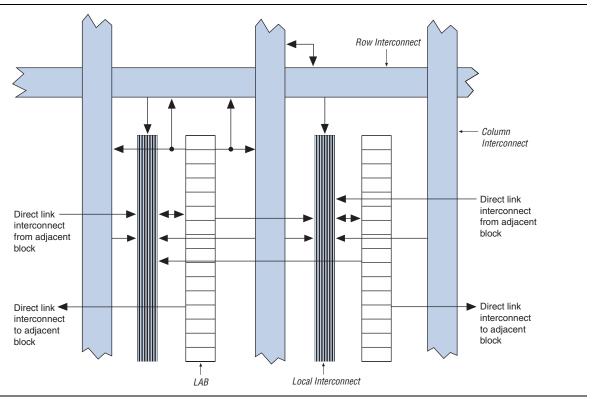

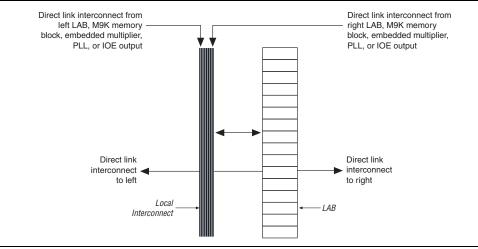

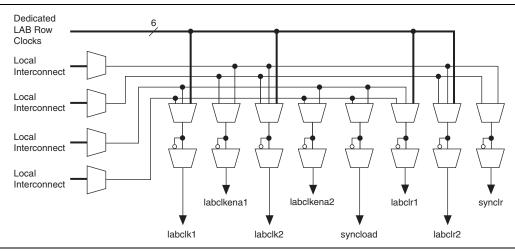

| LAB Interconnects                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 2–6    |

| LAB Control Signals                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 2–6    |

| Document Revision History                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 2–7    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |        |

| Control Signals                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 3–3    |

| Parity Bit Support                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 3–3    |

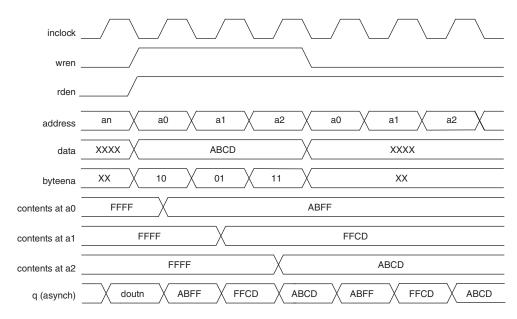

| Byte Enable Support                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 3–3    |

| Packed Mode Support                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 3–4    |

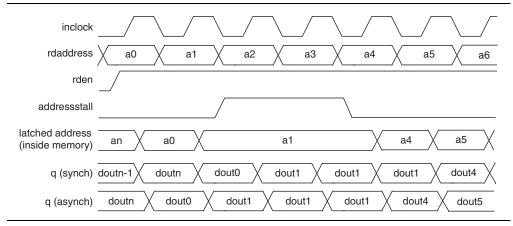

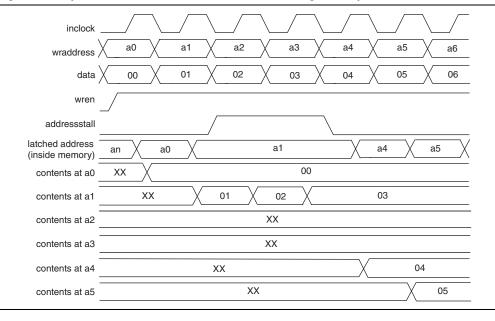

| Address Clock Enable Support                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |        |

| Mixed-Width Support                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 3-6    |

| Asynchronous Clear                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 3–7    |

| Memory Modes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 3–7    |

| Single-Port Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |        |

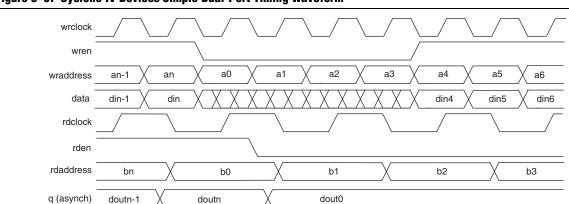

| Simple Dual-Port Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |        |

iv Contents

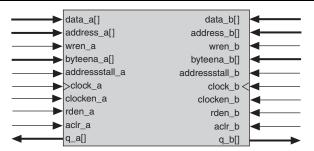

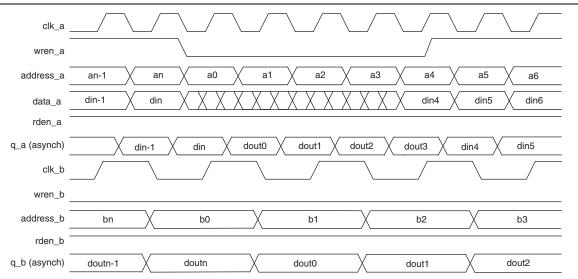

| True Dual-Port Mode                                      |      |

|----------------------------------------------------------|------|

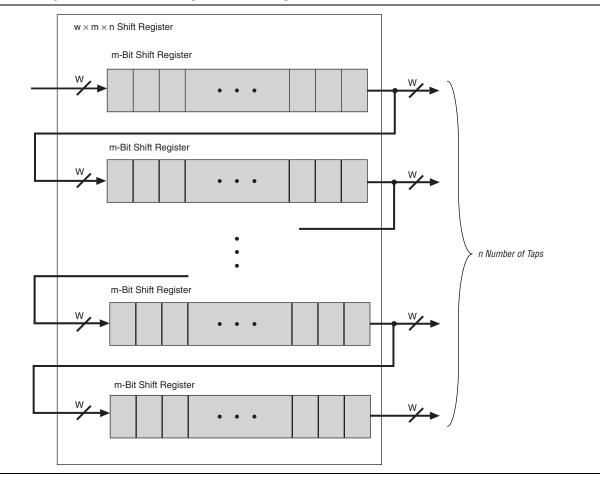

| Shift Register Mode                                      |      |

| ROM Mode                                                 |      |

| FIFO Buffer Mode                                         |      |

| Clocking Modes                                           |      |

| Independent Clock Mode                                   |      |

| Input or Output Clock Mode                               |      |

| Read or Write Clock Mode                                 |      |

| Single-Clock Mode                                        |      |

| Design Considerations                                    |      |

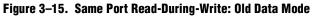

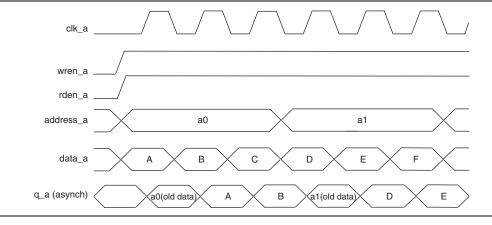

| Read-During-Write Operations                             |      |

| Same-Port Read-During-Write Mode                         |      |

| Mixed-Port Read-During-Write Mode                        |      |

| Conflict Resolution                                      |      |

| Power-Up Conditions and Memory Initialization            |      |

| Power Management                                         |      |

| Document Revision History                                | 3–18 |

|                                                          |      |

| Chapter 4. Embedded Multipliers in Cyclone IV Devices    |      |

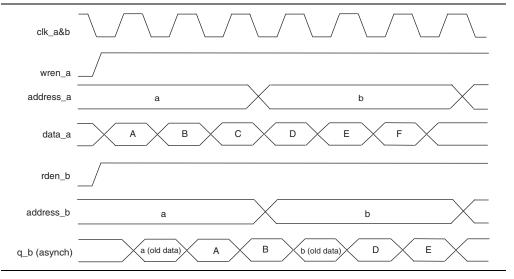

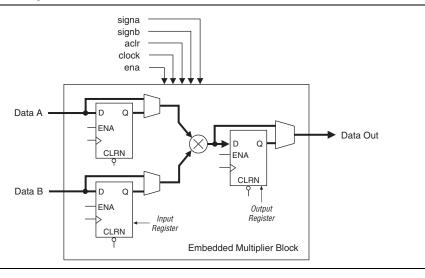

| Embedded Multiplier Block Overview                       |      |

| Architecture                                             |      |

| Input Registers                                          |      |

| Multiplier Stage                                         |      |

| Output Registers                                         |      |

| Operational Modes                                        |      |

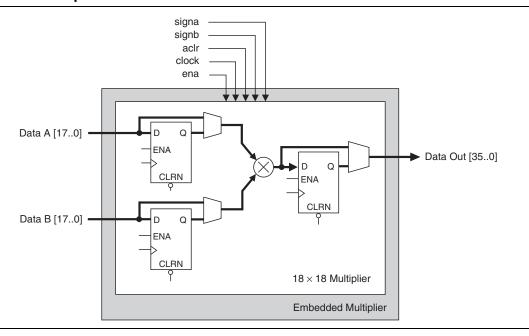

| 18-Bit Multipliers                                       |      |

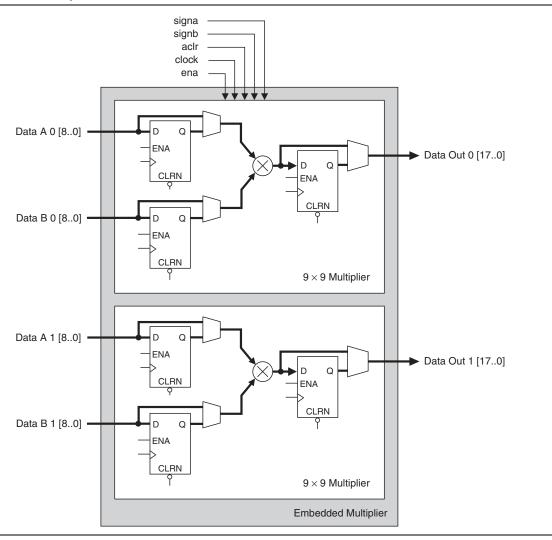

| 9-Bit Multipliers                                        |      |

| Document Revision History                                |      |

|                                                          |      |

| Chapter 5. Clock Networks and PLLs in Cyclone IV Devices | - 4  |

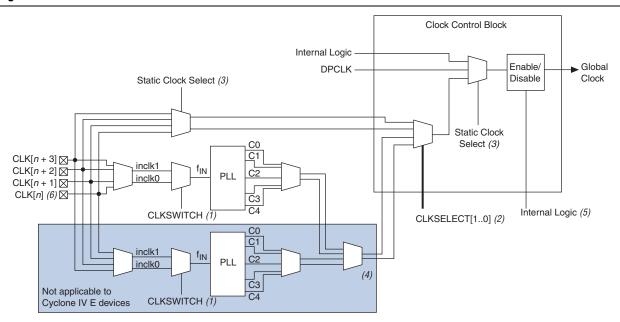

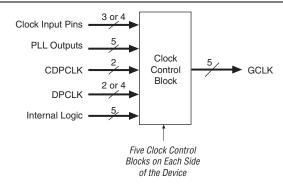

| Clock Networks                                           |      |

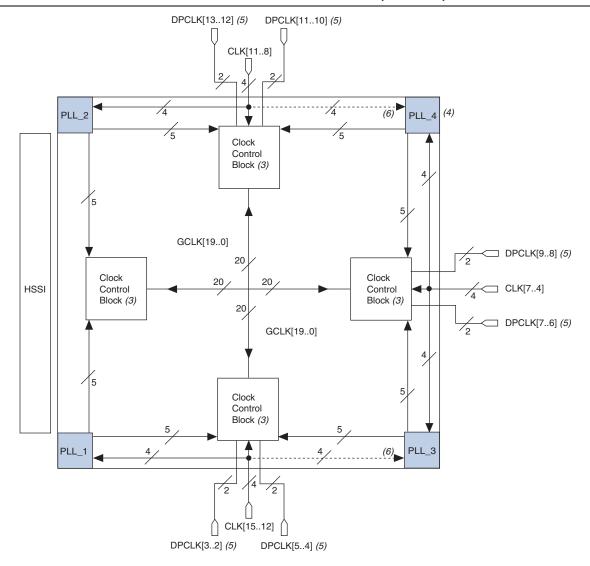

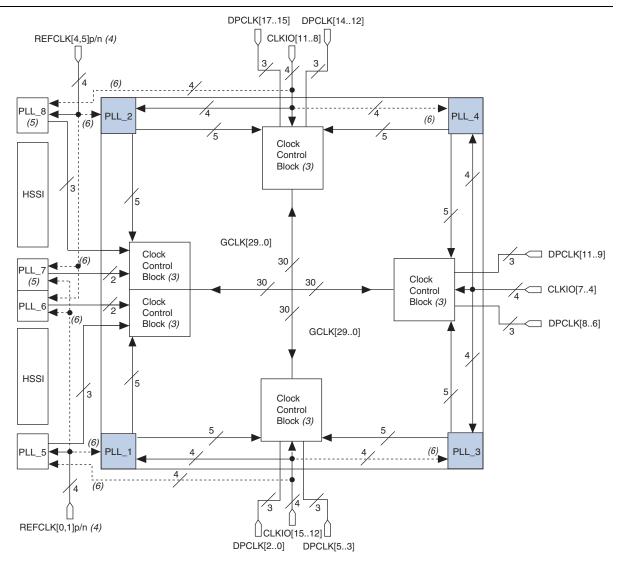

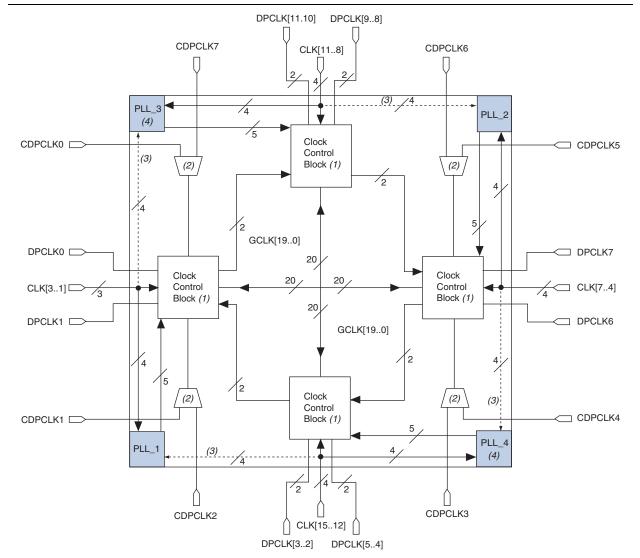

| GCLK Network                                             |      |

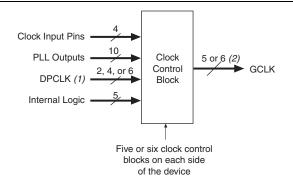

| Clock Control Block                                      |      |

| GCLK Network Clock Source Generation                     |      |

| GCLK Network Power Down                                  |      |

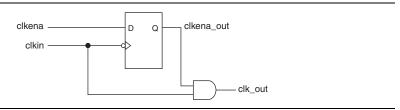

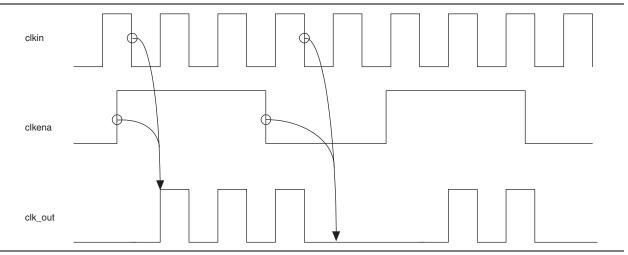

| clkena Signals                                           |      |

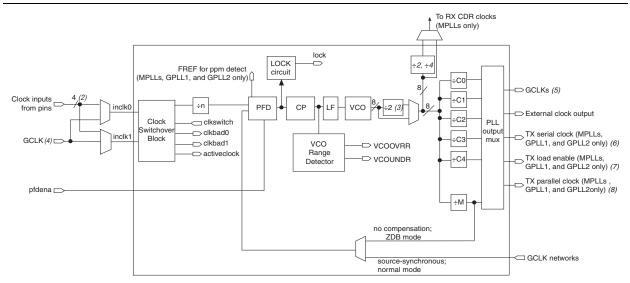

| PLLs in Cyclone IV Devices                               |      |

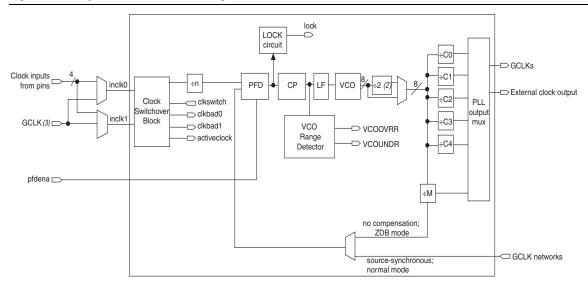

| Cyclone IV PLL Hardware Overview                         |      |

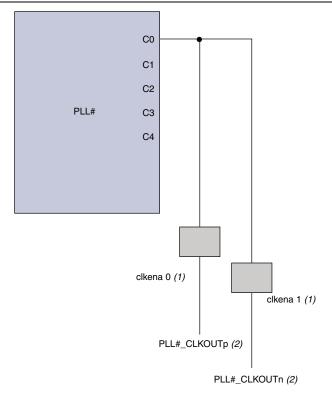

| External Clock Outputs                                   |      |

| Clock Feedback Modes                                     |      |

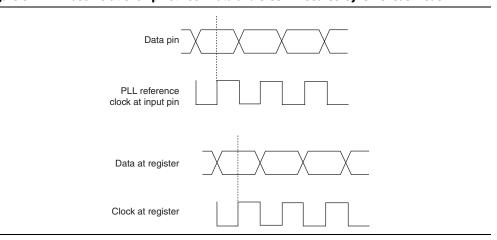

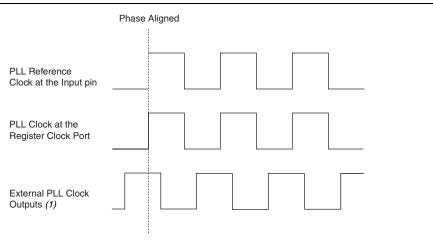

| Source-Synchronous Mode                                  |      |

| No Compensation Mode                                     |      |

| Normal Mode                                              |      |

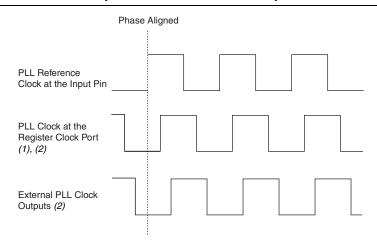

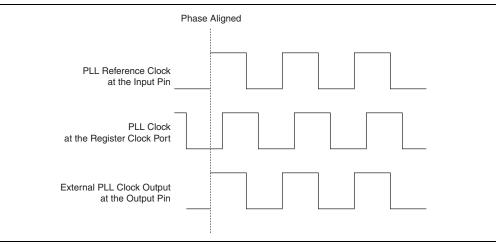

| Zero Delay Buffer Mode                                   |      |

| Deterministic Latency Compensation Mode                  |      |

| Hardware Features                                        |      |

| Clock Multiplication and Division                        |      |

| Prost-Scale Counter Cascading                            |      |

| Programmable Duty Cycle                                  |      |

| PLL Control Signals                                      |      |

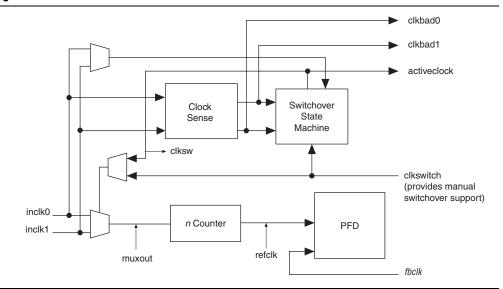

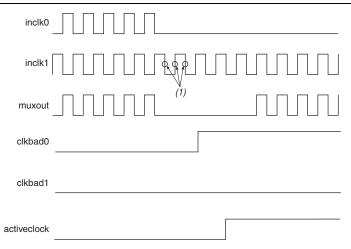

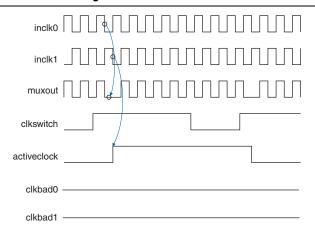

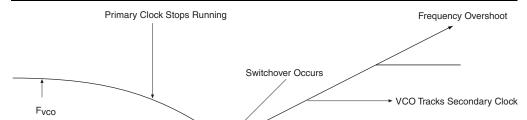

| Clock Switchover                                         |      |

| Manual Override                                          | 5–29 |

| MATHIALL MELLICE                                         | 7-/9 |

| Manual Clock Switchover                                              | 5–30 |

|----------------------------------------------------------------------|------|

| Guidelines                                                           | 5–30 |

| Programmable Bandwidth                                               | 5–32 |

| Phase Shift Implementation                                           | 5–32 |

| PLL Cascading                                                        | 5–33 |

| PLL Reconfiguration                                                  |      |

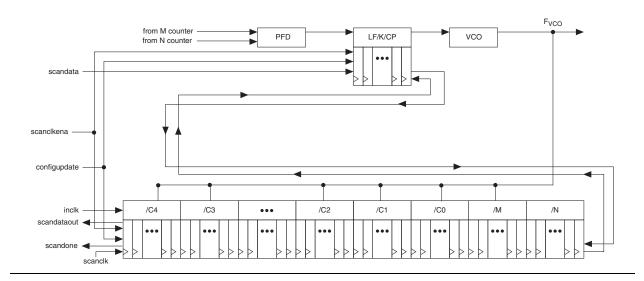

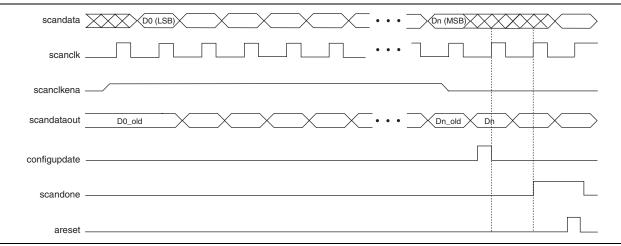

| PLL Reconfiguration Hardware Implementation                          | 5–34 |

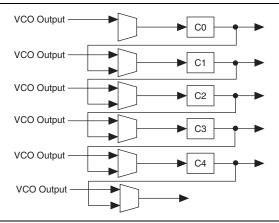

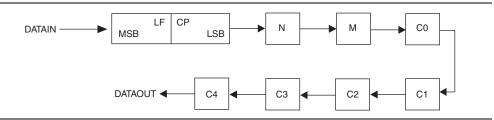

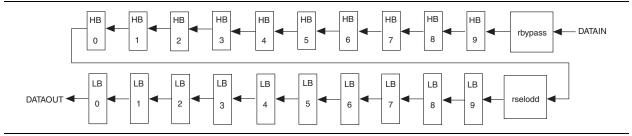

| Post-Scale Counters (C0 to C4)                                       |      |

| Scan Chain Description                                               |      |

| Charge Pump and Loop Filter                                          |      |

| Bypassing a PLL Counter                                              |      |

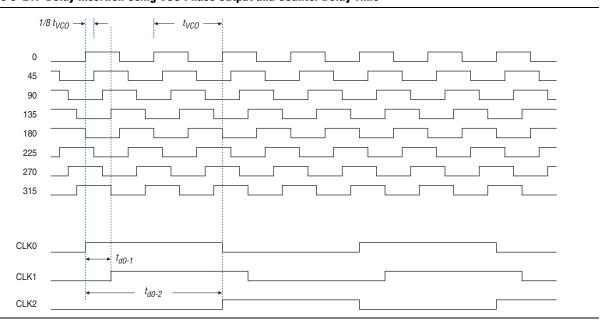

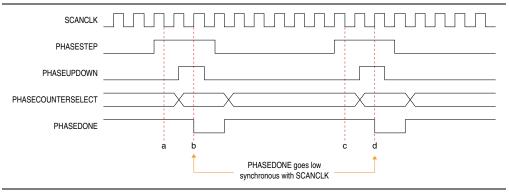

| Dynamic Phase Shifting                                               |      |

| Spread-Spectrum Clocking                                             |      |

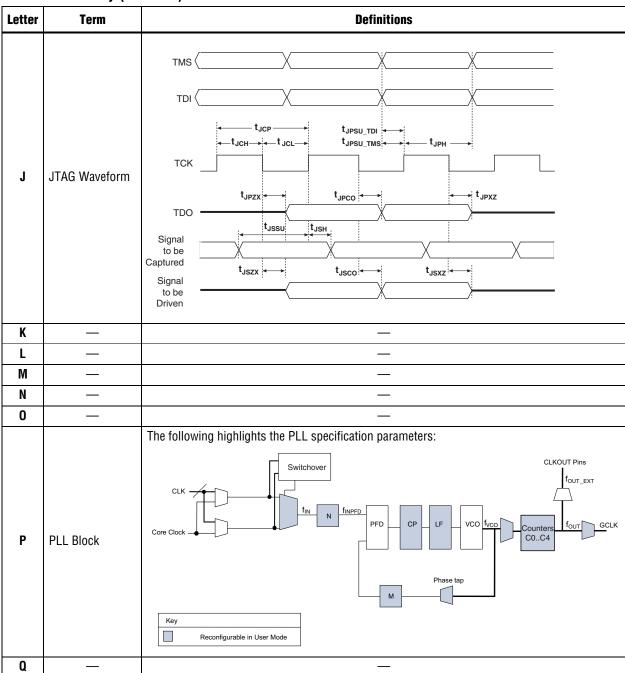

| PLL Specifications                                                   |      |

| Document Revision History                                            |      |

|                                                                      |      |

| Section II. I/O Interfaces                                           |      |

|                                                                      |      |

| Chapter 6. I/O Features in Cyclone IV Devices                        |      |

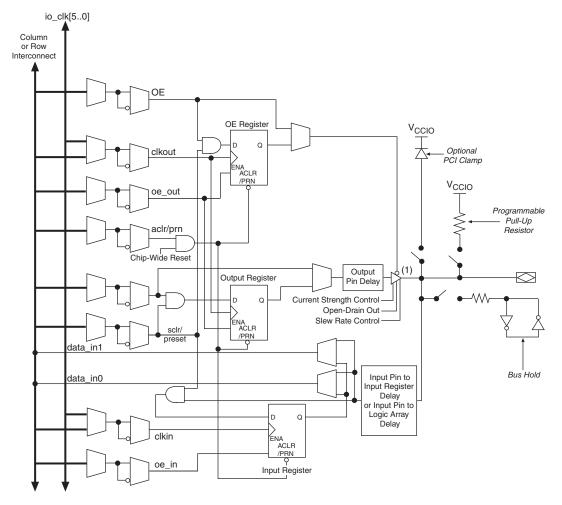

| Cyclone IV I/O Elements                                              | 6 7  |

| I/O Element Features                                                 |      |

|                                                                      |      |

| Programmable Current Strength                                        |      |

| Slew Rate Control                                                    |      |

| Open-Drain Output                                                    |      |

| Bus Hold                                                             |      |

| Programmable Pull-Up Resistor                                        |      |

| Programmable Delay                                                   |      |

| PCI-Clamp Diode                                                      |      |

| OCT Support                                                          |      |

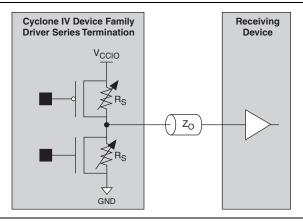

| On-Chip Series Termination with Calibration                          |      |

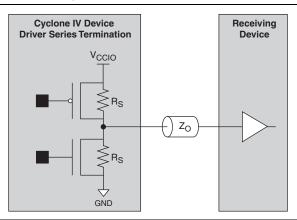

| On-Chip Series Termination Without Calibration                       |      |

| I/O Standards                                                        |      |

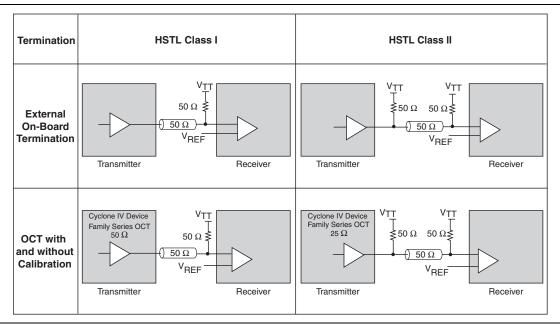

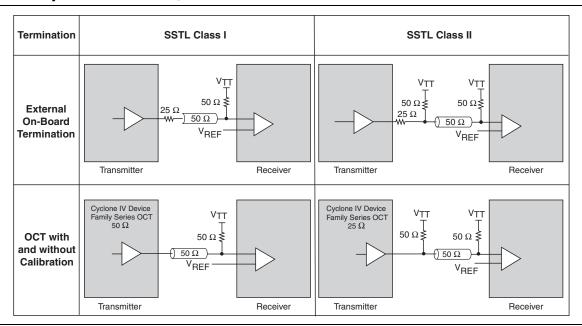

| Termination Scheme for I/O Standards                                 |      |

| Voltage-Referenced I/O Standard Termination                          |      |

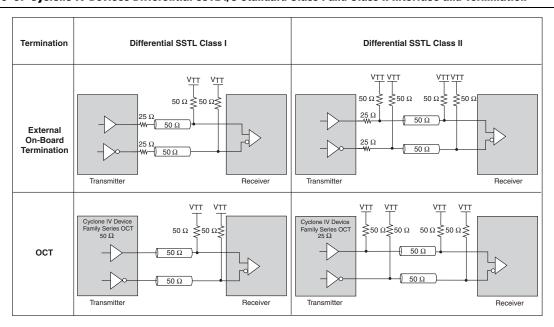

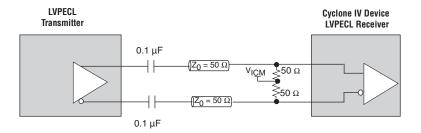

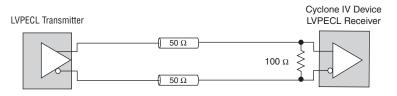

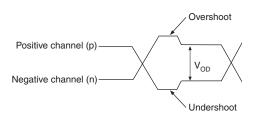

| Differential I/O Standard Termination                                |      |

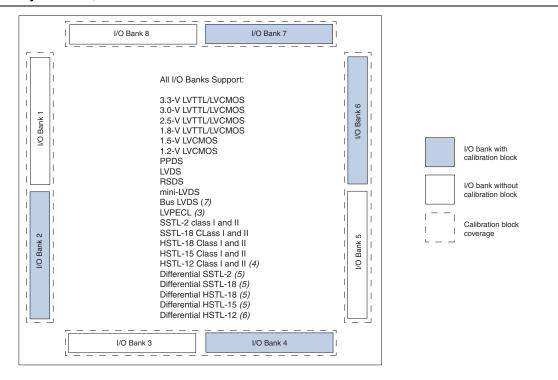

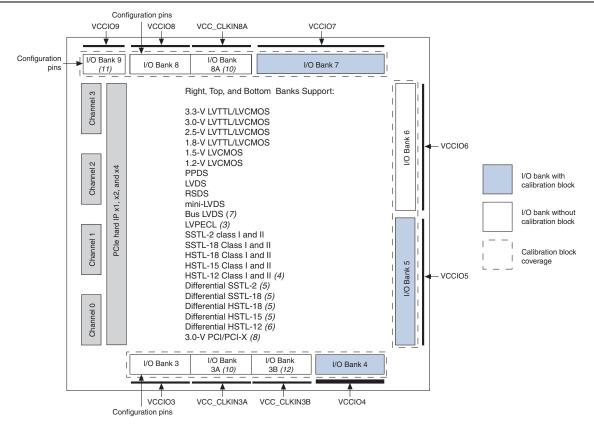

| I/O Banks                                                            |      |

| High-Speed Differential Interfaces                                   |      |

| External Memory Interfacing                                          |      |

| Pad Placement and DC Guidelines                                      |      |

| Pad Placement                                                        |      |

| DC Guidelines                                                        |      |

| Clock Pins Functionality                                             |      |

| High-Speed I/O Interface                                             |      |

| High-Speed I/O Standards Support                                     |      |

| High Speed Serial Interface (HSSI) Input Reference Clock Support     |      |

| LVDS I/O Standard Support in Cyclone IV Devices                      | 6–29 |

| Designing with LVDS                                                  |      |

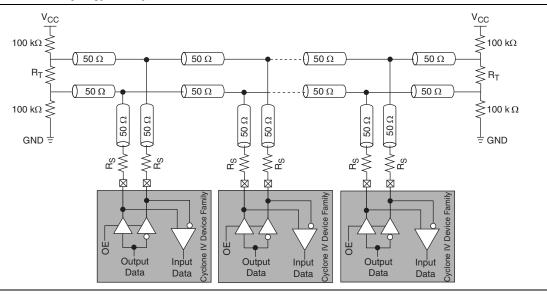

| BLVDS I/O Standard Support in Cyclone IV Devices                     | 6–30 |

| Designing with BLVDS                                                 |      |

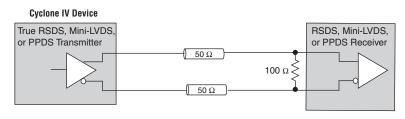

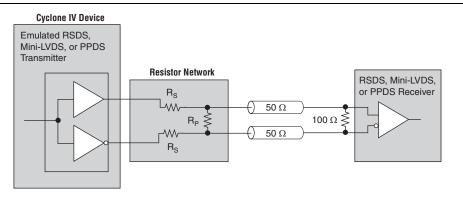

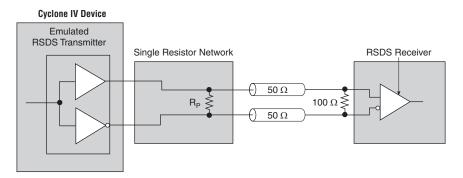

| RSDS, Mini-LVDS, and PPDS I/O Standard Support in Cyclone IV Devices | 6–32 |

| Designing with RSDS, Mini-LVDS, and PPDS                             |      |

| LVPECL I/O Support in Cyclone IV Devices                             | 6–34 |

| Differential SSTL I/O Standard Support in Cyclone IV Devices         |      |

vi Contents

| Differential HSTL I/O Standard Support in Cyclone IV Devices                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                        |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|

| True Differential Output Buffer Feature                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                        |

| Programmable Pre-Emphasis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                        |

| High-Speed I/O Timing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                        |

| Design Guidelines                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                        |

| Differential Pad Placement Guidelines                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                        |

| Board Design Considerations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                        |

| Software Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                        |

| Document Revision History                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 6–39                                                                                                                                                   |

| Chapter 7. External Memory Interfaces in Cyclone IV Devices                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                        |

| Cyclone IV Devices Memory Interfaces Pin Support                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 7.2                                                                                                                                                    |

| Data and Data Clock/Strobe Pins                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                        |

| Optional Parity, DM, and Error Correction Coding Pins                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                        |

| Address and Control/Command Pins                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 7_12                                                                                                                                                   |

| Memory Clock Pins                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                        |

| Cyclone IV Devices Memory Interfaces Features                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                        |

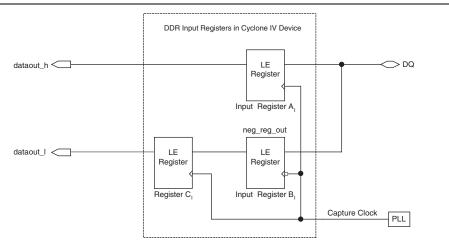

| DDR Input Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                        |

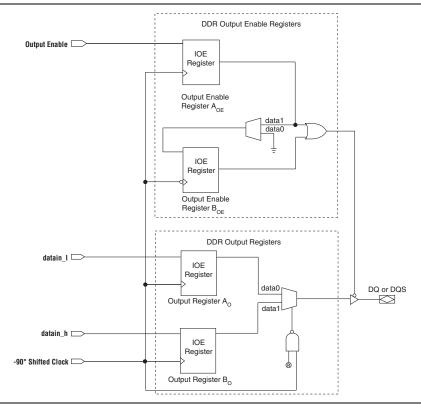

| DDR Output Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                        |

| OCT with Calibration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                        |

| PLL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                        |

| Document Revision History                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                        |

| Document nevision initiony                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                        |

| Chapter 8. Configuration and Remote System Upgrades in Cyclone IV Devices                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 8–1                                                                                                                                                    |

| Configuration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                        |

| Configuration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 8–2                                                                                                                                                    |

| Configuration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 8–2<br>8–2                                                                                                                                             |

| Configuration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                        |

| Configuration Configuration Features Configuration Data Decompression Configuration Requirement Power-On Reset (POR) Circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                        |

| Configuration Configuration Features Configuration Data Decompression Configuration Requirement Power-On Reset (POR) Circuit Configuration File Size                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                        |

| Configuration Configuration Features Configuration Data Decompression Configuration Requirement Power-On Reset (POR) Circuit Configuration File Size Configuration and JTAG Pin I/O Requirements                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 8-2<br>. 8-2<br>. 8-3<br>. 8-4<br>. 8-4                                                                                                                |

| Configuration Configuration Features Configuration Data Decompression Configuration Requirement Power-On Reset (POR) Circuit Configuration File Size                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 8-2<br>8-2<br>8-3<br>8-4<br>8-4<br>8-5<br>8-6                                                                                                          |

| Configuration Configuration Features Configuration Data Decompression Configuration Requirement Power-On Reset (POR) Circuit Configuration File Size Configuration and JTAG Pin I/O Requirements Configuration Process                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                        |

| Configuration Configuration Features Configuration Data Decompression Configuration Requirement Power-On Reset (POR) Circuit Configuration File Size Configuration and JTAG Pin I/O Requirements Configuration Process Power Up                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                        |

| Configuration Configuration Features Configuration Data Decompression Configuration Requirement Power-On Reset (POR) Circuit Configuration File Size Configuration and JTAG Pin I/O Requirements Configuration Process Power Up Reset Configuration Configuration Configuration Error                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 8-2         8-3         8-4         8-5         8-6         8-6         8-6         8-6         8-6         8-6         8-7                            |

| Configuration Configuration Features Configuration Data Decompression Configuration Requirement Power-On Reset (POR) Circuit Configuration File Size Configuration and JTAG Pin I/O Requirements Configuration Process Power Up Reset Configuration Configuration Initialization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 8-2<br>8-3<br>8-3<br>8-4<br>8-4<br>8-5<br>8-6<br>8-6<br>8-6<br>8-7<br>8-7                                                                              |

| Configuration Configuration Features Configuration Data Decompression Configuration Requirement Power-On Reset (POR) Circuit Configuration File Size Configuration and JTAG Pin I/O Requirements Configuration Process Power Up Reset Configuration Configuration User Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 8-2         8-3         8-4         8-4         8-5         8-6         8-6         8-6         8-7         8-7                                        |

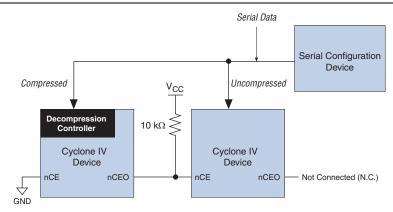

| Configuration Features Configuration Data Decompression Configuration Requirement Power-On Reset (POR) Circuit Configuration File Size Configuration and JTAG Pin I/O Requirements Configuration Process Power Up Reset Configuration Configuration User Mode Configuration Scheme                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 8-2         8-3         8-4         8-4         8-5         8-6         8-6         8-7         8-7         8-8                                        |

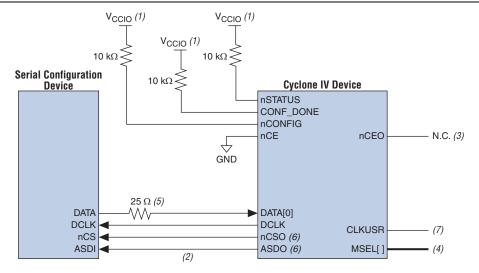

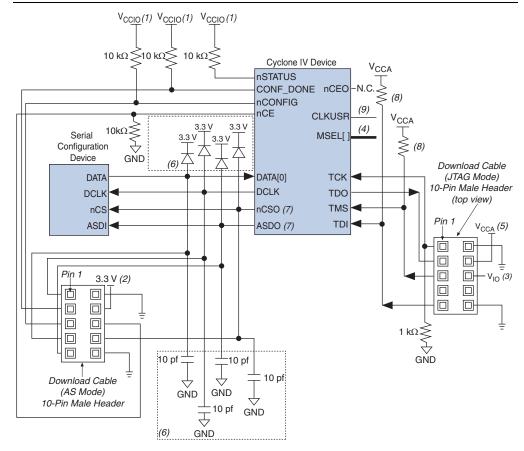

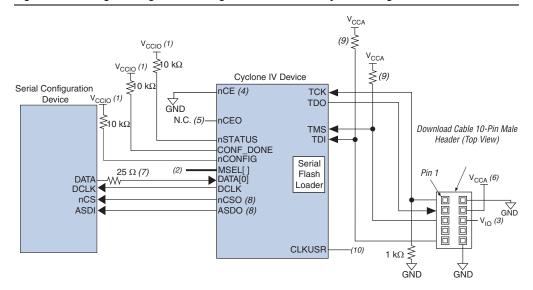

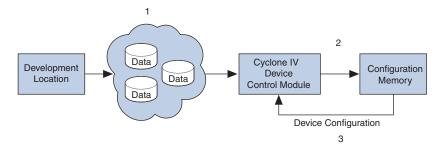

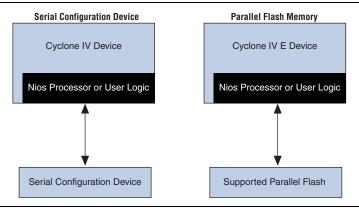

| Configuration Features Configuration Data Decompression Configuration Requirement Power-On Reset (POR) Circuit Configuration File Size Configuration and JTAG Pin I/O Requirements Configuration Process Power Up Reset Configuration Configuration Configuration User Mode Configuration Scheme AS Configuration (Serial Configuration Devices)                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 8-2         8-3         8-4         8-5         8-6         8-6         8-7         8-7         8-8         8-8         8-10                           |